【FPGA/CPLD】 XILINX/ALTERA/Lattice/Actel #24 [無断転載禁止]©2ch.net

■ このスレッドは過去ログ倉庫に格納されています

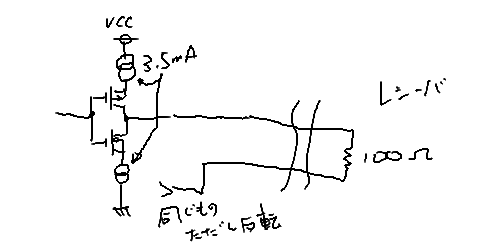

>>748 >>747 は さまざまなI/Oを使えるようにしているから、 http://www.altima.jp/column/fpga_edison/io_std.html ついでに、入力ならIO電圧は関係ないことも多い >>751 の訂正です。 LVDS33なんてあるんだな LVDSって、SelectIO 部分で、1つの信号を非反転Buffer 反転Bufferに入れて >>757 オペアンプは、いらんだろうが、 LVDSのドライバって俺が知ってるのはこんなのだよ。 >>757 >>768 >>773 >>772 そりゃ今はしょうがないべ ブロックRAMへステートマシンをインプリメントするってヤツみたいなもん? > MRLDの回路構成はニューラルネットとも相性が良いことから、今後は人工知能(AI)の用途も狙っていく。 新しい技術とは? これに対抗してFPGAの値段が下がってくれるとこっちはおいしい xilinxから手鏡を貰ったのだが、おっさんしかいない職場に手鏡を配ったって使わんやろ…… FPGAを淘汰できるくらい使いやすいデバイスだと俺はおいしい >>790 altera de10-nanoについて教えて頂きたいです >>792 FPGAにWebの動画を再生させていたってことか? de nanoは本体のromにマニュアルとLinux保存されてて、USB Ethernet経由でそいつにアクセスできるみたいな仕組みだったはず へーそうなんだー Linux回すとかなリ食うらしい 個人的にはssh程度で十分なんだけど、GUIあった方が新規増えるかもな Vivadoで訳あってBRAMを使わずにSliceのリソースだけで実装したいのですが、Synthesis Setting で-max_bram 0 にしてもわずかに消費してしまいます。 >>802 >>802 初心者なんだが昔に買ったDE0+Quartusで勉強してみたい >>806 >>807 DE0でも十分、8bitパソコン一台収まる位の規模までいける >>809 >>810 >>811 CPUコアから自作モジュール(Verilog)を呼び出して実行するのってどうやるのが一般的なんですか? 自分でFPGAのボード買おうと思うんだけどPapilio Pro LX9ってやつがいいの? それググれずに開発時のトラブルが解決できるだろうか >>817 >>816 MAX10 論理合成と、クロックのスキュー少し悪くないですか? FPGAって将来的に個人ユースで普及してくかな? 開発費が回収できないから、数が出ないのヤツはFPGA そんな事自分で判断できないレベルの人がAIのロジックなんか組めないw マクロで見れば永遠にニッチなのは当たり前だけど、 >FPGAとCPUのスピード比較ってないかな カップ麺の製造スピードと、クルマのスピードを比較しても仕方がない。 >設計によるとしか >>836 CPUが早いならソフト開発までで終わってオマンマ食い上げじゃ。 Clock Tree Performance for Stratix 10 Devices >>836 もう何年も速いデバイスは触っていないが、Ghzまで進歩したのか。凄いなとは思うがCPUが速すぎて >>840 ありきたりだが、アプリケーション次第としか言えんよな でも10コアが普通に3.3Ghzで動くからな。1.1G換算なら30コアだからなー。でも実質となると 既存CPUまたは、既存CPUでやっていることをFPGAで置き換えようとするような比較をすることが無理があると思うんだけど。 >>841 >>843 ■ このスレッドは過去ログ倉庫に格納されています