【FPGA/CPLD】 XILINX/ALTERA/Lattice/Actel #24 [無断転載禁止]©2ch.net

レス数が1000を超えています。これ以上書き込みはできません。

)())))())(()(())(()()(((()))))(()(()())(()(((()))))))))()((())())((()(()((((

)()))())((())()((((((()(()))))))()))))))))(()()()((((()()()((()))(()()(((()(

)))((()())((((())))(()))))(()))()(((())))()))))(())())((((((((()))()()((()((

)()())())()()))()()(()()()()))((()))((())((((()))()))())()))((((((()(()))(((

()()())(()))(((()))()))())((()(()((()()())())()()()(()()(()((())))))()((())(

(()(())()()(())()(()()))))()(((()()())(())()(((((()(())(()))))()((()))())())

())()()))()()()((()((((())(())))(((()((()(())())()))())()))))()()))()(()((((

((()(()((((()(()))))()))(((((()((()))))()()))()))())()(()()(((()()())())))()

())(()))()))))()())()()(((()))(()))((()((())()))))((((((()()()()()))()(()(((

())(()())()())())(())))()(()))()))()(()((((())()(())((())))((((()()(()(())()

(((()()()((())(()(()(())((((()))(((())()))))())(()))))))))(())))(()(()())(((

)(()(()(()()())()(()(())()()()()))))()((()()()()))()()(((()))((()(()()))())(

)()(((()(())()()))(())))))())()(((()())(())((())())(())())))()()))()((((((((

()()))))(()(()(((((((()()((((()()()(())(((()))()(()())(()(((()))))))))))))))

)))((()((())((()(())((())))(()()))()(()())()()(()(((())())())))(((())))(()()

()(()()(((((())()))((()()()(())()))))(()())(()))(((()))))(()()()(()))(()())(

)())(()())((()))()())(()))()((())))())()()))()())))()((((()()((())(())((((((

)((())(((()(()((((((())()())()))())())(())())((((())))()())(())))(((()()))))

((()())()((())(()((()()))())))((())()()())(()((())()(((())()())()))()())(())

(()())()(()())(()(())((()(((())((())))()())))))(()()()(()(())))((()()())()()

())))(()))))()(()(()(()()(()))()(())))))()((()())()(())((()))((()(()(()(()((

)((()(((())())((())()()))(((()(())(()())()())(((())())())()))))()()(((())())

(()()((((())(()((()))))()))()(()((())((())))(((((()))))()(()(()))((()())))))

)()()((())(((()((()))((())()()()(()()((()())(((())()))())(()()()))())(()))))

)((()()()()))())()))()()()((())))((())(()(((()())(((()()()())((())()(())()))

(()(()())))(()((()))((())))))())()())))))))(())()((())((((((())()()(((()(()(

)())()(()((())()())((())()()((()))(()()))(((((())((()()(()))()((())(()))))))

)()()))()())()(()(()()()()))(()()(((()))))))(()((()(((()()(()(())())(())(())

))()(()()()()())(()()(()()()(()(((()(())))()))(())()))()()())()())(()())((((

()))())))(((()((()()((())(()))(((()(())))()())()(()()()))()(())))())((()(()(

))(()((()))())())))()(((())(()()()())())()())())()))()((((())((())())()(((((

())(((())(()())))(((((((()(()))()))()()(()))((()()))(())()(()(())()))))(())(

)(()))(((((())((((()((()))(()((()()))(()()())())(())())))()(()())())())(()))

)))()((())(()(((())))))(()())(()((()()()(()((()))(((())()()))()))((())((()))

)(()((())())()))((((((())())((((((()())()(())(()))))))())()()(()())(()))(())

()()((()(((()(())())()()())))))(((((((()()()()))))())((())())))((()(()()))()

)(())(()()((()))(()())(())((((()((((()())))()())()()()))(()(()(())()())))())

())()))())))())())()(()()(((()())(()(()()))(((((()((())((()))()))))(())()(((

()((()()))((())((()()()(()))()(()(()()()))))()())))(()((()()()(()(()((()))))

)))(()())))))()(())()()((()())(())))(()((())))()(((((()())()())(()))(()(((((

))(()())))(()((())()(()))())))()((()()))(((()))()((((()()())(((()()())))()((

))())())(())()((()())(()()()))(()()()())))(()()(((())()(()(((((((()))))()())

()()(()(((()))((()))((((()()))))()(()))()()(())(((()(((())())())()((()))))))

())())))())))))((((()(()))((((((((())()(()))()(())((((()))()()()())())(()())

))((((((()))())(((())(((()())))(())()()()))()())(())(()))())(()()(()())())((

(((())())))()()((())(()()(()))()))))(((())())())((())()(()))()((())(()(((())

)()))((((((((()()))))()()()()()(()()())()))(()))((((()()()()()(()()()))())()

()))()())()()()))(())))()))(()(()((((()))))())((()((()))))))(((((((()((()()(

(())(())))()))))(((()(((((()()()()()(())((()()())))(()())(()()()(()))(()()))

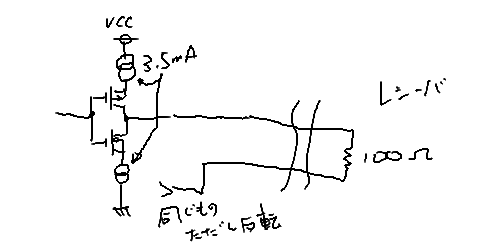

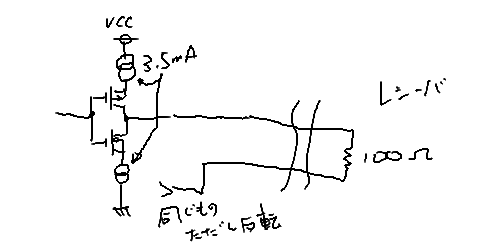

)()()(())))()))(()()(())))))(()()))(()(()())())(()((()))((())((((()(((((())) Max10だがSOFでは動作する。しかしPOFに書き込みすると動作しない。

しかしVerifyできるので書き込みは完了しているはずだ。

とするとPowerONでRamへのロードを失敗するのだろうと思う。接続している外部回路と

なにか関係があるんだろうか? >>2

ラズパイよりも扱いにくいですが、細かい所にも手が届きます 最近PCIバスの制御に興味が湧いてきたんだけど

Byte Enableって活用されてるの?

Byte Enableを使って1バイトだけ転送する使い方をする事はあるんだろうか 前スレの話。BGAに関して。

普通に人が住めるような温度、振動環境ならBGAでも良いだろうが、工作機械の中で使ったりするような物では駄目。

自動車の走行に関するような所にも駄目じゃないか? FPGAを始めようとしていますが、教えてください。

Xilinxの開発ツールには、

1. ISEデザインスイート

2. Plan Ahead

3. Vivado

の3つがあるようですが、どのように違うのでしょうか?

ISEが古くてVivadoが新しいようですが、Plan Aheadはどの位置にあるのでしょうか。

Plan Aheadは、ダウンロードする場所もわかりません。 >>11

雑に言うとvivadoの前身がplan ahead

iseは更新止まってるので今更覚える必要はない >>12

>今更覚える必要はない

VivadoってSpartanの開発できたっけ? >>13

コマンドラインなら、できるらしい。

Spartan7が出たら「できる」ということになる。

今のvivadoでは、出来ないらしいです。 Plan Ahead を初めて見たとき、それまでのISEの路線とは全く異なる画面絵作りで

ビックリした。たぶんどこかの会社をXilinxが買ったんじゃないかな?

で、Xilinxは もうPlan Aheadは推していないんでしょうか? 前スレの話題だけど

スマホなんかのBGAは小さいから、かかる応力も少ないよ

エンタープライズは筐体に余裕有るから排熱ちゃんとしてるんじゃないかな

電源切らないからヒートサイクルになりにくいのも有りそう

ゲーム機は排熱カツカツでデカイBGAなのが良くないんだろうね 鉛フリーと膨張後の急激な冷却でクラックが起きるのが原因

温度を上げないようにするかゆっくり冷やすか2択 いきなりVivadoだとびっくるするから慣れてもらうために

PlanAheadのGUIの皮をかぶせたらしい とは言っても、Plan aheadでも充分ビックリするGUIだよ。

ISEのときのあの画面は、どこにあるんだろう、って。

しかも、ISEに比べると、シンセシスの時間が長い。 アルテラしか使ったことないのだが、XlinxもCPUは無料の開発ツールでつかえるの

か? 以前は10万くらいのツールを買わないとつかえなかったと思うが、、 Vivadoは最新ツールだし重い

ISEは軽い

でもやっぱりVivadoはtclも使えるし楽だなぁ SDC (SynopsysR Design Constraints) XilinxだとCPUとかも全部無料なの?乗り換えようかな >>26

途中でティックル使って、長〜いパスを入力する根性があればね。

信じられんわ。 >tclなんかどういう用途で使うの?

alteraだとモデルシムでデバッグするときに使う。 そりゃASICやったこと無い人からしたら、tclなんてそこまで・・・と思うかも知れないけど

Vivadoは制約ファイルがSDC準処な訳で、出来なきゃ話にならんわ 前スレで出てた森岡さんの本持ってたわ

カバーがないけどw

でかい会社に行けば個人本棚で寝てるやつがいっぱいありそうだな 教えてください。

XilinxのISE 14.7 をインストールしたのですが、iMPACTが起動できません。

これまではISEの小窓からiMPACTをダブルクリックすれば、外部窓として起動したのですが、

今回は「_impact4.exeの起動に失敗しました」というメッセージが出てしまいます。

\ISE_DS\ISE\bin\nt (32bit用)だと起動するのですが、nt64だとダメです。

何か私が勘違いしているでしょうか。

よろしくお願いします。

Windows7 pro 64bitです。 とうとうx86にまで至ったか。

The ao486 is an x86 compatible Verilog core implementing all features of a 486 SX.??

https://opencores.org/project,ao486 森岡さんの本を何年か前に購入したけど、

初心者すぎてまだちゃんと読めるレベルに達してないです。

自習だとなかなかきびしいなあ。 >>39

代理店の、初心者向け無料セミナーを受講するのが早道かも bemicro max10はもう生産しないんかねぇ… >>41

10年後も言ってそう

MAX10のボードなんて高くないんだからさっさと買って物作りすりゃいいのに

安いボード買って積むのが趣味なんだろうけど Xilinx 9500って、なんであんなに電気食うの? MAX3000Aもクロック入れても入れなくても殆ど消費変わらなかったな

漏れ電流がほとんどなんだろうね 未使用部分は動的に回路から切り離して使用時に再接続とかCPUでやってるようなことを

将来はこっちも実装させられるのかな?

(切り離した部分にFPGAが電源供給切ってくれるようになること前提で) やっぱIGLOO2は消える運命かい?

ラティスのXP2とモロ競合してるんだが。 >>55

何がいいの?

市場の原理で決まるんじゃね >>56

どっちの見かけ上は同じ。

igloo2はフラッシュで直接スイッチしてるから完全なハード回路と同等に起動

XP2は内蔵フラッシュからSRAMにロードするからシリアルメモリからの起動タイプよりは

早く起動

肝心の能力差は遣ってみなけりゃ判りませんよね。

宇宙線への耐力も違いますよね? なんだよ 6入力のLE 450MHzって

IGLOO2でやっと4入力になったというのに。 原発のサソリ型ロボットってやっぱりFPGAなのかな。火星に行ったのもFPGA搭載だったし放射線に強いとかあるのだろうか。

ビットコインみたく計算ネットワークで相互監視させてエラー排除とかやれば高耐久になりそうだけど中の人はどうやって放射線耐久性を作り出したんだろう。 >>63

集積度高いのは根本的なとこで外部ノイズに弱いから、

現在のノイズ対策技術を施した設計で、昔の集積度低いプロセスで製造して、さらに多数決回路なんかで補完させるとさらに強くなるはず。

で分厚い鉛でカバーしてシールド。

こういうとこだと単機能に特化した低性能のものの方が良いはず。 CPU付のFPGAやってみたいがARMとNIOSならどっちやるべき?

おなじようなものか? > CPU付のFPGA

これなら、ARM以外の選択枝は無いと思うが。

ハードマクロのNIOSなんて あったっけ? 今のご時世NIOSなんぞ覚えても何の役にもたたん

あれはSoCなFPGAがなかった時代の遺物だろう >>63

宇宙線に強いのはアンチフューズだけど。

フラッシュとS-RAMではフラッシュが強いような気もするけど実際どうなの? >>66

ARMはハゲが買収したから死刑フラグでたわけだろ。 今はザイリンクスもZynq推しだし、やっぱりARMじゃないかね Xilinxならただで全部出来るぜ

Altera SoCはベアメタルのデバッガは有料 >>68

その昔はXにPowerPCが入ってた事もあるし、その逆でActelはソフトCPUのCortex-M1が使える。

NIOSもSoCより安いから良いもんよ >73

えっ、DEO-NANOって有料ツールがないと開発できないの? DEO-NANO買ってみようかと思ってたが有料ツールがないとFPGA部が触れないのなら

意味ないが、ベアメタルデバッグってどういう意味で使ってるんだろ? >>69

> SoCだと何がいいんだ?

FPGA SoCは意味無いと思う俺。

汎用SoC使って、足りないとこをFPGAにすればいい >>70

フラッシュのが回路自体のソフトエラーは無いから強いよ

FF自体は書き換わるのは同じだろうけど、

回路自体が書き換わらないなら何かしらできるしね

軍用とか航空、宇宙はActelのアンチヒューズが独占してるらしいな >>76

ゴメン、ARMコア入りFPGAの話な

Quartusの無償版ではLinuxターゲットしかデバッグ出来ないって事 Actel・・・もう無いんだがIntel言いたくない人と同じなのかね >>79

コイツ、何言ってんだ?

無償版で使えないのは、XiのChipScopeの方だろ >>81

は?最新のvivadoならロジアナも無料だよ そうか?、そりゃ悪かったな

ISEの終了と共にXi使うの止めたから、最新の状況は知らん

んで、>> Quartusの無償版ではLinuxターゲットしかデバッグ出来ない

これは、どういう意味だ。 >83

Linuxまで触るつもりはないが、FPGAの書き換えができないと意味ない。できるだろ。

それができるんなら、NIOSを載せてARMとも連携できるはずだよな。 >77

5$のラズパイを日本でもそろそろ売り出すらしいが、10$でもいいからMAX10

をのっけてくれんかのーw

だれか中国人をけしかけて、つくらせろよ。全くコンパチ品を作っても芸がないだろ

うにな。 >85

だからさー。ベアメタルってところが意味不明なのよ。具体的に例を挙げてみてよ。

Linuxを載せて、その上にアプリを載せてアプリのデバッグはできるんだろ。

何ができないんだよ。

FPGAの部分はVerilogで書いてデバッグできるんだろ。当然Niosだってのせることは

できるよな。 みたら、有償で当たり前のような かなり特殊なツールじゃねぇか

Xiは同程度の機能が無償なのか?

ありゃ便利だけど

このレベルになると、そもそもツールに無償のなんか求めないし

それでメシ食ってるヤツでも無い限り使わん

DEO-NANO-SOCで遊んでみようか ってレベルなら

余程の事でもない限り、無償のGDBとSignalTapで間に合う

違うか? もう一つ

>Altera SoCのソフトのデバッグはLinuxしか出来ない

これは何を指してるわけ、Windows(ARM判)上で走るソフトの事?

なら、そんなモンMS以外 誰も求めてないだろ

ツールがLinux判しかない、って意味なら そうかも知らん(調べてないけど)

EDA-ツールベンダはLinux対応が基本だからな、 別に不思議じゃない。

もし、この$995のツール必須なら DEO-NANO-SOCなんか誰も買わんよ

だが、ググれば 買って遊んでるヤツはたくさんいる

無くても別に困らないって事だろ ベアメタルのアプリが作れないってこと?

例えばオリジナルのブートローダーが作れない、とか、DRAMいっぱいまでFPGAが使うのでLinuxを走られる場所が無い、

とか、ARMの計算力だけ欲しい、みたいな物が作れないって事になるのかな?

Linux入れるとメモリとかストレージエリアとかそれなりに必要だし。

レジスタ直接アクセスするのにドライバ作ったりmmapみたいな余計なことしたくない、とかもあるか。 >>90

ベアメタルのアプリが作れないのではなく、デバッグ方法が提供されていないという意味かと。

自前でgdb stub作ればデバッグできるはず。 つかARM使ってたらDS-5知らないとかありえるんかね

というレベルのソフトなんだけどな・・・

そんな荒れるような話でもないと思うんだが >>92

Realview なら持ってるけど使えるかな? ARM使ってるがしらないよ。w それに荒れてないと思うが、、、 >>91 サンクス

あ〜なるほど。どこかでバイナリ作って実行はできるんだ。

でもバイナリ流し込むにしてもJTAG公開されてないとSDカードとかに限られないかな?

自前でGDB入れるにしてもJTAG使えないとUART経由とかか・・・

JTAGのサポートとかこの辺がDS-5無償版では制限されてる感じなのかな。

ひょっとしたらスタートアップ周りも自前になるのか。ARM HPCコアのスタートアップ自前でとなると大変そうだ。 >>95

SDカード経由ならできるはず。この場合はu-bootが起動するので、ここで止めてイメージをロードできると思う。、

以前購入を検討したとき、以下のような感じだったはず。

1. USB Blaster互換のJTAG I/F経由アクセスする方法->添付されているDS-5はこの方式、アクセス方法が未公開(?)

2. ARM Core用のJTAG I/F を使う場合 normalな2020 or 10 pinならCortexA-9用のJTAG ICEが使えるはず。ETM対応の38pinbの場合は、それに対応した\iCEが必要。 Zynq で FPGA だけ使おうと思っても勝手に ARM が動き出しちゃうんだよなぁ。

起動してすぐに SLEEP するように出来ないものか? >>96 たびたびサンクス

・ブートストラップとかはu-bootに任せて、自前のアプリだけ実行するのはOK。

けどデバッグ機能はろくに無いのでエイやで実行する感じ。

・SDカード以外のブートは無理

一度SDから立ち上げてオンボードのROMとかに書き込めば出来るかも。

u-bootのソースからHPC固有のブート部分だけ抜き出して、自前のアプリとくっつけるのも出来そうではあるね。

(そこが公開なのか?というのも調べないと…)

けどHPCの設定を変更したい場合、システムレジスタの設定はユーザの責任。標準u-bootのソースそのままは使えない?

Niosみたいに変更を反映したソースを自動生成してくれると良いのだが…というか、それも有償版DS-5の範疇か。

バイメタルアプリ作るなら素直に有償版買った方が早そうですね。 ベアメタルだw

ZynqはFPGAのコンフィグをARMからしかできないから、コンフィグ後に眠らせるしか無いのでは? 日本だとZynqでベアメタルやITRON系だ! っていそうだよな >>98

それな

もともとZynqってA9にArtix-7やKintex-7をつないで

1パッケージにした物なんだから単体の物を買えば良い話 >>94

ARM純正の環境知らないで草生やすとか・・・

Keil MDKも知らない言い出しそうだな >>98

たまたま小さいボードが安かったから。

http://www.trenz.jp/products/te0722/

digikey で買ったけど、結局無駄になった。 Zenqの入門でもっともやすくてLinxが走るの紹介して DEO-NANOとZenqBerryはどっちがおすすめ? 全てを見通してわかってる風に茶々いれる口数が多いやつほど何も成さない法則 >>108

そういうレベルの質問をここでする人がZynqいじるなら

いらんところではまっても解決できないだろうから

多少高くても純正品に近い扱いのZedboard買った方が良い

ここの人はIntel(Altera)推しが多い印象だから人に聞きたいならそっちでいいんじゃないかと思うけどな たしかにXiは宣伝が派手だが蓋を開けてみるとガタガタってことがいままでしばしば

あったな。 DE0-Nano-SoC $99

http://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&;CategoryNo=167&No=941&PartNo=1

Zybo Zynq-7000 ARM/FPGA SoC Trainer Board $189.00

http://store.digilentinc.com/zybo-zynq-7000-arm-fpga-soc-trainer-board/

デバイス単体なら、どちらが勝ってる とか言い難いが、

ボードレベルだと↑だ、比べれば判る Zynqはアカデミックで買えるならいいけど一般価格で買う気には?

>>86

むしろArduinoこそ突然の電源断でも何も問題ないけどスペックで見劣りするから

FPGAで補強しようとか考えるところないかしら 先に上げたのは

どちらもFPGAベンダーの、代表的なボードメーカーの製品

公平な選択だろ

俺が上げたのより、安いってのはその通りだけど

端子が配置がPi互換ってだけで、

Piのイメージで動くわけじゃないから、大した意味無いよ

PiもFPGAも使った事ないのか? そんなんだからZedboard推してるのにドスルーなのな

開発環境入れたら最初から色々設定はいってるし

ネットの情報も多いから、安いからとかそういう理由で

変な物買って積むくらいならちゃんと勉強できるものを

買う方が最終的に投資に対する効果が高いよ

あとZynqBerryは持ってるけどメーカーが用意してる物が

少し特殊だからはじめの一枚には全くお薦めできない

形が同じってだけでピン互換な訳でもないし、互換にして

使うならばRPi買えばいいし何をしたいのかという話

何か目的があるとか、既に色々経験があってSoCも試しに

触りたいというならいいと思うけど、そうじゃないなら

FPGAならFPGAのみ、ARMならARMのみの環境を

ちゃんと使いこなせるようになってからSoCに手を出すべき

やること、やれること、覚えることが多いからいきなり

手を出すと訳わからなくなるんじゃないかな >120

確かに。仰せの通りだな。しかしやっぱり流行りのも使ってみたいなー。

それにARMだから特殊ってことないだろ。PICやHEW系ならよくつかってるから

ARMも新しいPICくらいにしか思わんけど、、どうせCでプログラムするだけだし。

FPGAは殆どAlteraしかつかったことないし、そもそも普段は使わない。たまに

つかう。まあでも適当に使いこなせていると思う。

Piは今ちょうど勉強中でapt-getで何とか使ってるレベルだな。

Linuxにくわしくないのよ。Windowsなら.netなら自由にプログラム組める

けどC#とかVBとか.netの範囲でね。

今一番やりたいのは何かというと、LinuxでIOを叩きたい。高速転送がやりたい

FPGA部にレジスタを配置して、レジスターにライト

FPGAからの割り込みで、FPGA側のIO(メモリー)をLinuX側のDDRにDMAしたい。

PiではFPGAを外付けしてもこういうことはできないからね。

SOCなら出来そう。できないとSocの意味ないな。 これからMICO8を始める漏れにはワケワカメに盛り上がってるね。 >>113

>いらんところではまっても解決できないだろうから

どれが良い?って聞く人では小さなSoC FPGAの問題も解決できなんじゃなのかなって気がするよな どんな問題を想定してるの?

具体性が示せないのではだめだろ。経験値があるなら具体的に的確に表現

できるもんだよ。「気がする」てのは占いレベルだろ。 >DEO-NANOとZenqBerryはどっちがおすすめ?

どちらがおすすめな気がしますか

占いレベルでおすすめ教えてください PowerPC使わなくてもコレどうですかって言ってたねXilinxは

FPGAだけも辛いから汎用SoC市場も考えるって言ってたのがZynq

Zynqのシリコン出来る前の話だから今は知らないけど Pi-Zero $5 とか出されたからなぁ

これだと、乗ってるARM-SOC $2 ぐらいか

秋月の中クラスPIC 程度の値段だから

FPGA-SOCとか、売る方にとっては厳しいよな Picの10000倍の性能があって同じ値段ではやってらんないよ。

しかし売る方だけじゃないよ。

Piは成熟してきたからね。Linuxの障壁が無くなったし、そのLinuxが

Openソースで驚異的難度のソフトを素人がapt-getですぐにダウンロードして

組み合わせて使うことができる。

画像認識、音声認識なんて最先端の成果をこともなげに使えるからソフト屋も

FPGA屋もおちおちしてられないよ。

たとえばCQ出版のインターフェースに載っていたがきゅうりの選別装置なんて

恐らく同業者は驚異に感じたと思うよ。普通に開発会社に見積もりさせたら3000万

くらいは余裕だったと思うが、これみたら100万くらいでやる奴だって出てくるかも

しれない。((((;゚Д゚))))ガクガクブルブル

特にFPGAなんて金取れるところと言ったらまあ画像処理だけだろ、ある日

Pi用の汎用GPUの乗ったIOが500円で売り出されてしまったら、いままで1000万で

受注していた画像処理の仕事が日曜大工並みの値段になってしまう。

((((;゚Д゚))))ガクガクブルブル

うどんか蕎麦屋でも始めた方がいいかもな。

すまん夢の無い話で、、、きゅうりの選別装置をみて小便ちびりそうだった。

ショックだったよ。おおおお俺の仕事がなくなっていく、、、、。 研究者だっておちおちしてられないよ。きゅうりの選別って一寸した研究レベルの

ことだものな。1億の予算を取って、今日はその研究の成果を発表しようと思って

ふとインターフェースをみたら、まったく同じことをド素人が発表してる。

てなことになると、「ショボイ研究しやがって、1億返せ」ってことになりかねん

からな。 結局、使いこなせる人が少ないだけなんじゃねぇの?

そこまで必要な特注案件も少ないだろうし >>130

zynqは成功してると思うよ。

cpuとfpgaを別々に実装してた頃には戻りたくないね。 ID:UdLWMfG4

なんだこの句読点が使えない奴は?

日本語の勉強からやり直せ vivadoの最新版はロジアナ、シミュレーション、高位合成が無償バージョンで開発できる。

自作IPもaxiバスでarmコアから簡単に制御出来る。

一昔前じゃ考えられないくらい

便利になったと思う。 NIOSとかソフトCPUは2個くらい載せることできるんだろか? こんな所にも句読点先生わくんだなw

>>132

もともとニッチなところを埋めるデバイスだしね。

俺の業務では採用例はあるけど、自分自身では治具とか

プロトタイピングにしか使った事無いな。

量産品だとコストを含めてFPGAじゃないと困るという

場面は実際少ないからなぁ。勿論作るものによるけど。

なんとなくホビーな人は、凄い事が出来そうな魔法の石だし

何かこれを使って面白いこと出来ないかな、とか漠然と

考えてる人が多そうな印象なんだよな。 >139

そうなの? CQのmax10の雑誌に付録でついて来たやつで、一寸これから

ためしてみる。

spi のデバイス ADとかDDSとかDAとか5,6chあってそれに

16chほどUARTが必要なのだが、全部FPGAで組んで実装できないこともないと

思うが、そこまでスピードもいらないので、2,3個NIOSをのっけて

レジスタを叩くだけの簡易ポートだけつけて全部ソフトでやろうかとも

思うのだが、こんな考え方ってあり? CQのmax10だと、微妙だなぁ

安くもないし、規模も小さいし 加えてConfigも怪しい

なんでそんなもん買ったんだ? って感じ

まぁ痛い目に会ったぶんだけ、勉強になるから無駄にはならないよ。 これを規模小さいというのか? 腐るほどリソースがあってどう料理しよう

かと悩んでるが、、、 それなりの、測定器/予備バーツ等 持ってりゃ大丈夫だろうけど

↓あたりを見ておいた方がいいぞ、それなりのベテランでも痛い目あってるから

実物は持ってないが、これなら俺でも嵌る

http://nahitafu.cocolog-nifty.com/nahitafu/2016/05/max10-70b8.html ソースついてくるから、ライタで書き込んだ方が楽そうだな。

一通りそろってるから、入門用には良さそうな感じしたけど落とし穴有るね。 もう、既にぶっ壊してんじゃない?

あまりの苦情に、後続ロットで対策講じたのかどうかは知らないが

USB端子が付いてるから、全員とは言わないまでも 8/10 ぐらいは挿しちゃうよな

それでPICが逝ってしまうんだから、むしろ嵌らない人の方が凄い CQ編集部には技術や居ないから、ナンチャッテ技術やのウンコ設計基板を読者に使わせると

判明してからは技術屋さんはCQの出版物なんて完全無視でしょ。 マニュアルもろくに読まない自称凄腕が何か言ってるな 寺は「USBブラスターモドキ」とのセット付録を良く許したな。 初心者は本とかじゃなくてterasicでボード買ってラーニングロードマップ通りに練習するのが一番いいと思うよ。英語だから敬遠したくなるかもしれないけど、初心者向けにかなり丁寧に書いてくれてる 英語の習熟度によるよなあ。

ブンガクと違って技術用語は読みやすいって言っても、程度の差はあっても自分のネイティブ言語ほどはすんなり入ってこないだろね。

わかりにくフレーズに遭遇したとき、同じ言語能力でも、内容について学習できている人は、文脈から解釈しやすいけれど、

そうでもない人は余計に苦労する。

ブンガクと違って読みやすいって言ってる人も、実は、内容のことをある程度わかっているから解釈しやすくなっているだけこともある。

初心者は、その内容にアテを付けることが難しい。

少々内容にまずいところがあっても、とりあえず日本語の書籍でざっくりした知識や体験を積むと、英語の資料も読みやすくなるし。

できている人は、できていない人がなぜできないのか、なかなかわからんものだよな。 その日本語の資料が糞みたいな物しか無いから英語のを

読む方が良いって話なのにねぇ

基本データシートも英語読めないと話にならないし

いちいち言い訳して逃げちゃう人は向いてないとしか

言えないけどナァ 電子部品のでーたーシートが英語だって? あんなの英語ではないよ。

といいつつも、中国語のでーたーしーとはお手上げだよ。 USB blaster II って クロンでてないね。USB BLASTER よりは安いたって諭吉が数人飛ぶよ 今は、アングラのcheap boadでも usb-config 乗せてるからね

もう単体での需要が殆ど無いんでしょ >>157

英語だよ。だけど日常で人間が話してる英語ではない。 そんなことよりスレタイ古いままぢゃん

>XILINX/ALTERA/Lattice/Actel

罪鈴楠、淫照、裸丁酢、微小蝉 だろ >>162

ついでになんとなく一つ買ってみたけど持ってるボードが

みんなUSBから焼けるから使った事無いんだよな・・・ >>162

ピックつこうてるんはモドキのパクリやろ >>164

パクリはわかってるんだけど

今度MAX10(NIOS入り)の仕事のヘルプが振られそうだから

絶対数が足りないのに買ってもらえないんで

自分専用に在ればいいなと。

バイトブラスターなら余ってるんだけど

今どきパラレルポートを増設するのもばからしい >>165

わかってるならなんで質問を?

万一動作がおかしくてもモドキにすればいいんだからどうにでもなるでわないかいな

自分で一から作る部品代よりもアマゾンで中華買うほうが安いんだから。 >>166

胡散臭いものを買う言い訳をみんなに聞いてもらいたいんだよ

そのくらい察してやれよ $5 なら、さっさと買って試せばいいじゃん

何なの? この人

もっとも CHINA POST だと、何時来るか解んないけどな

或いは、永遠に来ないかも

そっちの方が痛いか >>170

モドキではない奴なんだね。クロンの方だね。 >英語の習熟度によるよなあ。

最近英語の勉強を始めたが、英語を覚えるのは楽やな。Verilogみたいな糞言語を

使ってるせいで無茶苦茶かんたんに思える。

Verilog、VHDLこの巨大糞何とかならんのか?w サイクロン10が発表されたみたいだけどスレ的にはどんな感じ?

1.2Vが使えるからエネループが使えるっぽいけど FPGAってバッテリー駆動どうなん?

マイコンだと800μAで動いたりするけど

バッテリー駆動の製品皆無だからやったことない LEが6kから、EQFPも有りそうだから 安物ねらいか

興味があるのは、価格くらいだな 大飯食う癖に仕事のスピードは遅いし、使いにくいし、、、、 >>175

IGLOOやIGLOO2の土壇場だよ。SRAMつかってないからね。 なんか最近今まで話題にもなってなかったmicrosemi推しの人いるねw

LatticeのiCE40系は腕時計での実績あるけどIGLOOは

どんな採用事例があるの? terasicからDE10のレビュワー/デバッガー募集のメールが来た 高位合成は、普及して行くのだろうか。。

もう、みんな使ってるの? >183

demo youtubeを聞いた。ナレーションが可愛いので最後まで聴いてしまった。

この英語は一寸中国訛りがあるんかな。時々口が縺れたりして無茶苦茶可愛いな。

イクスペンション ヘイデューってなん? とおもったらイクスパンション

ヘッダーのことだった。男が訛ってると山に帰れと思ってしまうが、女の訛りは

可愛いいな。 DE10

Lite 事かと思ったら Standard だって、オレがReviewしてやるよ

既に似たような製品出してる

名称が紛らわしい

HSMイラネ USBモドキを組み立てる気でしたが、心が折れました。

400円(送料込み)のを買うことにします。 FPGAの開発環境ってやっぱウインドウズが安定してるん?

linuxとかのmacつかった開発環境の安定性

どんなもんかおせーて? Lattice の開発環境が エンタープライズ版推奨で

ubuntu とか centos でちゃんとうごかないんだけど

どぅーいうこと?

なっとくいかんくない? XのはUbuntuで普通に使ってるぜ

オプソのものならともかくオフィシャル環境でMac版のあるメーカーなんてあるっけ? >>190

microchipのFPGAって使ったことないけど

どうなん? >>190

xってXILINXのことなん?

詳しくおせーて? >>191

microsemiの間違いかな?

SmartFusion2のボードなら買ったけど確かLinux用は

ライセンスだかなんだかの問題で使えなかったのと

大人の事情でZynqを使わなくてはいけなくなったので

積んでるわ・・・って何でこれを俺に聞いたのかw

>>192

Xilinxの事ね

詳しくって手順通りインストーラーで入れるだけで動いたし

ドライバーとかも特にハマる要素は無かったけど・・・

Ubuntu 16.04 LTS 64bitね

まだ勉強中だから深く使えて無いけどWindows版との

違いは特に思いつかなかったかなぁ 前に書いてた人がいて試してみたけど、ubuntuだとWindows(x64) よりも

短い時間で synthesize-map-route ができるみたいだね >>193

Xilinxの開発環境はフリーで使えるん?

入門用のXilinxのチップっていくら位から買えるんかおせーて? 罪のFPGAはプログラミング用のメモリーが糞高い

今は改善されてるのかな? >>195

つhttps://joelw.id.au/FPGA/CheapFPGADevelopmentBoards

Xilinxの開発環境はフリーのはデバイス限定だけど使える

つーかホームページに書いてあるレベルなんだからその位は

自分でggrks そんなんじゃボード買っても何もできないぞ >>196

竜宮城に行ってたんだね?

10年以上前の Spartan-3E くらいから標準のSPIフラッシュ

つなげるようになったはず latticeのverilogで

ポート出力をON OFF したいんだけど

出来無い たすけて!

どうすればいいん? っていうか書き込み電圧間違えて3.3V

のラインに5V流しちゃったんだけど

もうだめかな?

だからポート出力書き換えてもへんかしないんかな? latticeでの

verilog の書き方が詳しくのってるページとかおせーて? 悪いことはいわん そんなレベルならArduinoでも使うんだ https://twitter.com/ankyo3/status/834402964785618944

F1というマイナーな機種で3D初代をFPGAで作った。このときは自分が最高責任者だったので辛かった。

一応製品になったけど。ZG2はいろいろな意味でひどかった。

短命でむしろ助かった。あれはマネージメントが駄目。 >>204

PICとかは慣れてるから原因がわかるけど

初めてのチップはLチカまでが勝負じゃい PIC

で、ビルトすると、シンタ × エラー ってメッセージがでました。

シンタって誰? >>205

あんがと

>>209

構文エラー? どこでエラーが出てるか表示されてないん? >>210

ネタに構ってくれてありがとう。

漏れもこれかららティ巣はじめるんよ。よろぴくね >>207

分かりないのは当たり前で、

自力で調べるなり出来るのが大事だと思うよ bemicro max10はもう生産しないんかねぇ… latticeでようやくFT2232の自作書き込み機でようやく書き込みでけたw

情報少なすぎw

なんだよ嵌りポイント多過ぎだろ 人其々だろうけど、正直 lattice を選ぶ理由が思い浮かばないな

パッケージ、値段

それとも Config が趣味とか? おれは配線の引き回しが適当すぎたせいで、線間クロストークによる

影響でターゲットとの通信がうまくいってなくて、それに気づくのに

若干時間かかって嵌ったけどそれ以外はすんなりいった FPGAはマイコンに比べて敷居は高めだから素直にボードを買いなさい いまどきのデジタルオシロって時間軸を100msくらいにしても

数十KHzくらいの周波数じゃエイリアシングなんて起こさないよな?

そんなぼんくら設計ってFPGAつかうやつらはふつうしないよな? 知恵遅れにこの話しても通じなくて参ってるんだが?

エイリアシングについてもわかってないし

もしエイリアシングが起きてるなら計測器側の信頼問題だから使い方もきをつけなきゃいけないし

情報の共有が必要なのにそういった認識のない知恵遅れ相手にすんのもう疲れたw

まじつかえないw >>223

ネット上にのってる配線図がちゃんと配線されてる図面がないし

信号レベル供給用の配線部分の図が載ってない

FT2232がわのデータシート追わないといけない >>226

自分は秋月のページの資料で十分わかったけどなぁ >>222

そう思って

Brevia2 Booard Development Kitを買ったのだが、CDついてこない。基板だけ。

テクニカルサポートは無くなってる。

ispVMもないし、どうにもならん。

昔大倉電子にコケにされたから罪は使いたくない。

知らずにメメックにコンタクトして又してもコケにされたからね。

寺は野崎って野郎が担当してたんで使いたくない。

旧悪はタイ米は炊いてボード刈田けど、どうにもならん。 DDRメモリを繋げようとするともっと悩む事が出来るぞw >>230

補正プログラムぐらい数行で書けるだろ? 矯正下着は数枚重ねても漏れの内臓脂肪は抑えられない。。。 倉庫の隅から発掘してきたようなのを在庫処分セールする季節になったけど

古すぎて仕様がわかんないから手が出せないw アナログがICE2000を放出するとかいう話ない? https://goo.gl/MFkghn

これ本当だったら、普通にショックじゃない?? 組み込みで大容量でバックアップしたいのだが、インターフェースが簡単で且つ高速

というのはなに?

例えば

容量 1Gバイト

転送速度 1Mバイト/sec〜10Mバイト/sec

くらいでいいんだが >240

SCSIって媒体はなに? ハードディスク?

>241

SDカードはIFを作ってるところがあって使ったことがあるんだがシリアル転送で

SPIとかI2cとかでチョット遅いんだよね。

でも最近ウルトラSDとかあるので、ああいうのを使うのがいいのかな? ファイル・システムまで入れると、マイコンは避けて通れないから

それに付いて議論するつもりは無いけど

単純に読み書きだけなら、 ↓辺りを見てみれば

10Mバイト/sec 程度ならいけるんじゃないかな

試してたわけでは無いけど、ソースコードも公開されてるし参考にはなると思うよ

http://bitcraft.mydns.jp/embedded/sdcard/sdcard.html >>242

> SPIとかI2cとかでチョット遅いんだよね。

1〜10MB/sならSDかーどで十分 ファイルシステムかぁ・・・そういや、最初からファイルサイズがMAXの

ファイルを作っておいて、データ部分だけ弄る(FATやらディレクトリの

操作は一切しない)っていうのがあったっけな。 SDの10Mb/secってかいてあるのは、10Mビット/secのこと? それとも10Mbyte/sec

のこと? Bitだよね。 紛らわしいなw。調べてもどっちかわからん。w

大体は大きく見せるためにbitだよな。 腹立つことにどこのメーカーも10MB/secて書いてあるが、ビットなのかbyteなのか

わからん。メモリーの場合はほぼbit転送速度でワードの場合はワードって書いてある

な。BPSだとビットパーセックだよな。B/secはどっちのケースもある。 PCの通信規格ならBitにbyteだけど自分も明確に記述されてるのは確約は取れなかったので「速度の基準となる「1倍速」はコンパクトディスクの転送速度である150KB/secを基準としている」から計算してください。

っていうかウィキペディア先生にそこまでは書いてあるんだから古い規格知ってるならそらですぐ計算できるんじゃね?

俺はにわかなのでそんな規格なんか気にしたことないしそもそもFPGAにSDのバスを載せようと努力したこともないからわからん わかった。w B/secはByte/secだな。

これだけスピードがあるのに市販のSPIタイプとかは遅いよな。 普通は

MB/s = Mega Byte per sec

Mb/s = Mega bit per set >>251

正規に契約を結ぶか流出した仕様書読めば分かる事だけど、SPIモードはSDカードのスピードクラスを守る必要なんかどこにもないんだけど…?

あれは”対応しているハード上での”最小保障速度だから、お情けというかどうしようもない時用のSPIモードはマジいつでも削除していいおまけなんだけど?

ただ一応対応しておいてね、が今まで残ってるだけ。 >>252

逆だったか、書き込ませてしまってすまん >>239

組込のwifi経由でクラウドに保存とかで

どれくらいの速度がでるんかな? >>255

環境依存がひどい。

WiFiルータを持つ人がたくさん寄ってくると絶望的。 SDの4ビットモードはsimplifiedの規格書でも

十分実装出来る範囲書いてあるよ、FPGAだったらCRCを

バス毎に取っても楽勝だし。利用に関しては知らん >利用に関しては知らん

それが最大の問題なんだな… >259

あかん。最近こういう文章をみても「英語かー。萎える」とか思わなくなってきた。

以前なら「日本語で書けよなー」と即座に反感を持てたのだが、なぜか平気で受け

付けてしまう。それにしても国語が侵されてるなーとは思う。なんせ英語だと無料

で読めるものが非常に多いのでついつられて読んでしまう。圧巻はTEDだな。

こういう講演が無料なので、いつの間にか聞きふけっている内に次第に英語に

汚されてしまう。版権の切れた小説などは全部無料だものな。これでは英語漬けに

なってしまうよな。 >>263

大丈夫。 そのうち日本語もわからなくなるから。 CQのFPGAの電子工作に48MhzからPLLで50Mhzを生成するようになってるが

何のメリットがあるん? はじめから50Mhzつけたらいいだけでは? >>266

該当記事を読んでないがUSB付てたらそこに48Mhz必要じゃない? bemicro max10はもう生産…あ、あれ?ページが無くなってる… Cyclone10のボードどこにも売ってない・・・そりゃチップ出荷してないからw

今年後半らしいけど何月頃になりそう? Intel 絶不調だからな

のんびりと、サイド・ビジネスやってる暇無いだろ >>266

あのタイプの3.3V発振器ですぐに秋月で買えるのが48MHzですよ。 MAX10でLVDSでクロックを入力するときは、VCCIOは絶対に+2.5Vにしないといけないのか? データシートとピンアサインガイドを見たのですが、該当記述が見つけられなくて…(汗 >>270

減価償却済プロセスで安く作るシリーズだから

20nmの減価償却が終われば回ってくるんじゃない? FPGAのFFとか回路構成がノイズで書き換わったことある?

ソフトエラー端子あるけど、運用でエラー見つかったことある? 放射線あててみればw

誰かverilogスレ立ててよ次11だっけ? ファミコンとFPGAで遊んでたら面白いことになったんで、のせていいですか?

これクリアするには心の眼が必要です!

CHRROMのタイミングかなあ。

https://m.youtube.com/watch?v=30JgvMOJ_2k >>283

これFPGAでNESエミュレータ作ったんじゃなくて、ROMの方を作ったってこと? >>284

そうです。NESはファミコンの本体の機能で、カセットをFPGAにのせてます。将来的にはディスクシステムみたいにファミコンを拡張できるもにする計画です! 前も同じようなヤツがいたな

CPUのバグを指摘されても、結局 見つけられなかったんだろう

そのまま放置になったようだけどな 緊急!ワンタイム書き込みしちゃったみたいなんだけど

FPGA を間違ってワンタイム書き込みで書き込した場合って

もう二度と書き込みできなくなるん? ワンタイム書き込みしてない同じチップのは

書き込みテスト何回もできる

でもワンタイム書き込み間違ってしたチップはなんかい書き込しても

エラーがかかる

もしかしてやっちゃった? ってか、外付けROMじゃないFPGAって今はほとんどないんじゃない? >>290

MachXO2 には OTP (One Time Programmable、 ワンタイム・プログラマブル) ヒューズがあり

これのこと! >>292

AlteraのMAX10、 Flash内蔵 >>294

One Time Programmable ってのがあるみたい

実験でコンフィグレーションいじってたら間違ってワンタイムをONにしてた >>293

まじか

LatticeにはOTPとしても書ける機能がついてるのもあるのか

だったらやっちまったんだろうな... >>297

Latticeは低価格で買い替えが簡単だから別にそんなに負担はないけど

コンフィグレーション設定でこんなに簡単にワンタイム・プログラマブル ヒューズ

がきれちゃうなんて。。。。

ショック!w >>295

MAXシリーズって元々CPLDだったのに、何で突然FPGAってことになったんだろうね?

MAX10 FPGA ってわざわざ書くのもいかがわしい。 >>299

FPGAとCPLDの差なんてあってないようなもんだろ MAXシリーズは内部構造的に、もうFPGAと言っていいんじゃないかな

お客さんがFPGAの名は知っててもCPLDは知らないって人も多いし、

違いの説明も面倒だから「小規模のFPGA」って説明してる >>302

超CPLDとか超々CPLDって呼んであげて。 Alteraの場合、以前はLUT形式のでも全部PLDって呼んでたのが

徐々にFPGAって呼ぶようになったはず

MAXは2あたりからLUT形式になったから、その流れでしょ fpgaとdacで200MHzの正弦波作れますかね? >>307

作れるけど、DSSチップ使ったほうが簡単そう >>307

どの位の歪率を要求するかだな。思いっきり歪んでパルスみたいになっても良い(というかパルスなんだけど)で良ければ簡単 周波数もスイープしたりしたいんだけどFPGAだと難しいそうですね。専用ICの方が簡単そうだ。 なぜ専用ICというものがあるのか考えれば自ずと答えは出るはずだが XO2のFTDIチップつかった書き込み機

自作って情報すくなくね?

webで情報あげておいたほうがよい? 情報も何も、公式にそのものズバリの回路図があるだろ >>313

今見ると少し記述が怪しいところが。。。

ご愛嬌ということで。 すみません。何かお判りになる方いましたら教えて頂けませんか。

XILINX ISE14.7のIsimをコマンドプロンプトから実行したいのですが

「動作を停止しました云々」と表示され実行できません。

ISE GUIからは起動できましたのでIsim.log内の実行コマンドを実行しているのですが駄目です。

Windows8.1 64bit

よろしくお願いします。 >>318

無事解決しました。ありがとうございました。 cyclone10 LPは安いだけで性能はたいしたこと無いのね > 消費電力が最適化された 60nm プロセスを採用した CycloneR 10 LP FPGA は・・・

CycloneV=28nmだったよな、 コスト最優先でプロセス後戻りしたのか? もしかしたらFinFETかも

でもMAX10は55nmだからいらないよね 65nmとか45nmが普通だと思うんだけどなんでFPGAって半端なプロセスルール使うの?

余分なコストかからないんだろうか。 cyclone10はGX:20nmとLP:60nmでプロセス違うのか

>>324

いやcyclone10 LPだけ(他はだいたい普通のプロセスサイズ)

MAX10はXORフラッシュ混載だから例外

CPUからチップセット用に転用した時にリーク電流対策強化した?から

Intel65nmは他社換算すると約60nmになるとかか??? stratix10 = 14nm

arria10 = 20nm

cyclone10 GX = 20nm LP = 60nm

max10 = 55nm

まーメリハリきいてるよね

Intelになって全部最新プロセスになるなんてことはなかったw やっとlinuxでlatticeの開発環境が安定動作して

書き込めた

ウインドウズでしかできてなかったから悩んでたけど問題解決 >>330

max10のページには、

"MAX 10 FPGAs are built on TSMC’s 55 nm embedded NOR flash technology, enabling instant-on functionality."

と書いてある TSMC使ってるところなんていくらでもあるでしょ

Intelは完全自社工場なんだっけ? >>332

「大坂城建てたのだあれ?」

「豊臣秀吉!」

「ぶー。大工さん」

トンチならトンチだと言えよ。マジかと思ったぜ。 教えてください。

BOOT_SELECTピン(以下BSピン)は、H/Lどちらでも関係ないのでしょうか?

マルツで買ったMAX10-FB基板でJ1(BSピンのH/L切替)を変えても挙動が変わりません。どちらも同じ動作をします

自分が考えている正解

BSピン=L:CFM0でコンフィグ→動作開始

BSピン=H:コンフィグしてないので停止状態

壊れてしまったのかな? 小型化の話はASICにかかってるのではなく、SoCとか

マイコンに既存の専用チップを追加する構成にすると

と言うのが抜けてる感じの話じゃないかなぁ >専用設計となるASICではコストが高く、ステレオカメラのパッケージに収まる基板サイズにもならなかったという。

意味わかんねえ 単に、デンソーが何時も使ってるASICベンダーでは

ゲート数都合ででかいパッケージしか選べなかった

若しくはプロセスの都合で集積度が低くて複数チップになったって話かも XC9572XLのコンフィグしようと思ったら、Platform cable USB2 が壊れてた。

秋月にHS2とかHS3とか安いのがあったので購入してみたが、XC95非対応だった。

Platform USB買い直しかなぁ、あれ4万ほどするからなぁ・・・ 4万じゃちょっとなぁ

ググれば、FT232 でやってる例も見つかる

それでも真似れば パラレルケーブルなら1万円くらいだったような。自作出来るし。 >>341

どういう症状か分からんけど、自分で修理したら? >>344

パソコン側にパラレルが無くて。。っていまさらパラレルでもないだろうし。

>>345

USBを認識しない(unknown device)なので、ez-usb側のファーム消失だとは思うけど、

その前に何度か認識しないときがあったので接触不良だと思ってます。

>>346

svfファイルに変換するのが面倒だったので、このスクリプトいけるかもしれないです。

(件のHS3がdigilent.adeptを使えばXC95も焼けるそうなので、svfファイルに変換するのがかなり面倒なので諦めてましたが

行けそうな気がします) >>347

それを言ったら今さらXC95でもなかろうて。 >>348

まあいまさらXC95ですよね。

チップ単価が安いのと大量に作った基板の保守もあるので・・ 無印XC95の頃、PlatformUSBもパラレルポートもぶっ壊したなw

両者ともVIO(3.3V)じゃなくてVCC5V突っ込んで破壊

あれこれ模索するよりヤフオクで買っちゃうのが良いと思う >>347

ez-usbって、ROMに書いてあるのは、デバイスIDだけ。

ファーム本体はパソコンからダウンロードするから、元々入ってない。

古いデバイスを相手にするなら、なんだかんだでパラレルも選択肢。

リアパネルには出てなくても、チップを搭載はしてて、

コネクタを繋げば使えるマザーがまだ見つかると思う。 >>352

EZ-USBはI2C EEPROMからファームウェアのダウンロードが出来るよ

ファームウェア書き直したら直るんじゃないかな

不明なデバイスになるのはUSB Type-Bの接触不良じゃないかと言う

気もするけど XC95は秋月のFT245RLで書き込みツール作った記憶があるなあ

XC95自体あまり使い道は無いんだけど >>355

5VのトレラントにXC95(XL)は必要だしなぁ・・ >>356

5Vトレラントなものが減ってきた。最近は、諦めて電圧変換用ICを使っています。

以前は、ispMACH4000シリーズも使っていたのですが。 最近は、5Vトレラント必要なら74CB3T系とか噛ませりゃイイや…

と思う様になってきた 最近は5Vトレラント必要なら、デジトラ噛ませりゃイイや…と思う様になってきた >>361

フォトカプラを代替できるデバイスをご存じなんですか、是非教えてください。 最近Zynq-7000の評価ボードでFPGAを勉強し始めたのですが、わからないことがあるので質問させてください。

reg [8*128-1:0] str = "Hello world\0";

みたいな感じでリテラルの文字列をレジスタ(?)に入れられる構文か何かはないでしょうか?

Verilogです。

説明下手ですみません。 フォトカプラでないとダメなところもある。そういう観点抜きに>>361が発言をしているのだとしたらみっともない。 >>364

アナデバとアバゴが出してる。

(今はブロードコムか) >>366

フォトカプラの代替部品で大丈夫な所がほとんど。そういう部品を知らずに>>366が発言をしているのだとしたらみっともない。 >>369

うろおぼえだけど¥0がだめでないかな

文字コードを直接入れればいい >>371

デバッグプリント的な使い方で文字列をシリアルで吐き出そうとしていて、

文字コード直接はいまのところ避けたいと思ってます。

こういうソフト屋っぽい手法がそもそもFPGAとマッチしてないんでしょうか。 >>372

文法的におかしくはないんだけど。

どんなエラーが出てるの? >フォトカプラでないとダメなところもある。そういう観点抜きに>>361が発言をしているのだとしたらみっともない。

>フォトカプラの代替部品で大丈夫な所がほとんど。そういう部品を知らずに>>366が発言をしているのだとしたらみっともない。

いまどきデジタルアイソレータの存在を知っていることが自慢になると思ってるなんてことはないですよね? >>372

そういう流儀があることはわかってるつもりなんだけど、すごくソフト的なアプローチだと思ってしまいます。

空きピンに特定パターンのパルスを出力してトレースすることが多いな… >>375

知識が増えてよかったね❗ >>377

>知識が増えてよかったね

どうやらそのようです。自慢になると思ってる人がいるらしいことは勉強になりました。

もうずいぶん昔に広く普及したものなのに。 >>374

エラーは出ないんですが、シリアルで送った時に文字化けしているので想定通りに入っていないのかと。

シリアルのエコーは動作するし、リテラルの文字列を一文字にするとその文字は送れているんですが、

2文字以上にすると全部化けます。

書いていて思ったのですが、質問したところ以外に問題点がある可能性があるので見直してみます。 ほかにも問題抱えているみたいだけど特殊文字について。

ModelSimで確認したけどやっぱり ¥0 はnull文字にならないので文字コード使わないとだめね。

ダイレクトに文字コード書くのはいやというのはわかるのでparameter定義して連接で結合するとか… >>380

もしよかったら、詳しく教えてもらえませんか。

レジスタの添え字の小さいほうから順に1byteずつ文字が入っていくイメージだったのですが。 >>382

str="Hello world" なら

str[7:0]= "d"

str[15:8]= "l"

str[23:16]= "r"

:

余ったら上のビットはゼロ。

"\0" は 8'h00 のはずだけど、modelsim が変なのは知らん。

ってかシミュレーションしてみたら? いや、ModelSimで試したってだけで、

verilogとして¥0はnullとして使えないはずなのです。

元質問の本筋から外れているけど >>384

「使えないはず」ってのは、何を根拠に?

IEEE1364-2001 の 2.6.3 Special characters in strings に、

\ddd A character specified in 1—3 octal digits (0 ≦ d ≦ 7)

ってあるけど?

iVerilog も通るけれど。 文字化けした。

"A character specified in 1-3 octal digits" >>383

それは知りませんでした。ありがとうございます。

シミュレーションはまだうまく使えないんですが、練習してみます。

あとこちらで試してる限り”\0”は8h0になってます。

環境によって変わるとしたらあまり使うべきではないのかもしれませんが。 >>381 が言うように本当に Modelsim が正しく動かないなら問題だからメンターに確認したほうがいいよ。まあそんなバグはないと思うけど。 >>385

ご指摘の通りでした。あやふやな記憶で発言してすみませんでした。 >>389

それはいいんだけど、Modelsim が動かないことが気になる。 移動しちゃったんで手元に環境ないけど以下のような感じだったはずです。

ModelSimPE10.3c windows (ちょっと古いのはご勘弁を・・・)

reg [39:0] chr_test = "ABC\0";

initial begin

$display("%s",chr_test);

$display("%h",chr_test);

$finish;

end

で、出力が以下の通り。

ABC

0000414243

\ddd が 3digit固定と勘違いしていたので"ABC\000"というのも試したけど同じでした。

適当な通常文字のコードにしたときは問題なく文字列表示も16進もLSB側に入っていました。 ModelSim IntelStarterEdition (10.5b) を入れて試してみました。

〜〜

`timescale 1ns/1ns

module null_test;

reg [39:0] chr_test = "ABC\0";

initial begin

$display("%s", chr_test);

$display("%h", chr_test);

$stop;

end

endmodule

〜〜

結果が以下の通りでした。

# ABC

# 0000414243

# ** Note: $stop : W:/work/null/null_test.v(10)

"AB\0C"とかしてみたら16進で 0000004142 となりました。

やっぱりNull文字周りの解釈がおかしいっぽいです。 >>370

言ってもただのトランスじゃねぇかよ... まあいいんだよ

極端な思考をする人はそっとしとけば >>394さんへ

>>370にアンカーを付けて

「言ってもただのトランスじゃねぇかよ」はどういう意味で言っておられますか? >>402

フォトカプラの代替品があるのに知らねぇのかよとドヤ顔で言ってるから何のことかと思いきや昔からあるパルストランスにちょっと毛が生えたような奴じゃねぇかよ、ってことかと 代替品とか言い出した奴がまずどの部品か提示してない件について パルストランスだと変調かけなければいけなかったり、事によっては符号化とか面倒な事が多そう。 >>403さんの推測はまあいいとして、>>394さんご自身の説明を聞きたいところです。

>>405

デジタルアイソレータって言葉や、代表的なメーカーは出てきてます。 デジタルアイソレーションの方法としては

トランス結合、磁気結合、光結合、コンデンサ結合の4種類かな? 5Vトレラントの話だったのに、いつのまにかアイソレーションの話へ >>408

トランスと磁気って同じ。光はPC。

PCを除けば二種類じゃね? 言葉通りのデジタル+アイソレーションならリレーもありかもしれないけれど、

いわゆるデジタルアイソレータという部品には含まれないと思う。

DLPみたいな感じで、MEMSのリレーが出てきたらわからないけど。

トランス結合とは違う磁気結合のものがあるんだと、今、初めて知った。

デメリットも含めて、割とこれがフォトカプラ代替に一番近いかも。

>>411

話題の変遷は

5Vトレラント→フォトカプラ受け→デジタルアイソレータ

かな。

アイソレーションなしで良い用途にデジタルアイソレータは勿体ないですね。高価だし電流も喰うし。 >>413

非常に広義で考えるならともかく、

「絶縁できるトランス」とは「コイルが2つ以上あるもの」を指す

ということであれば、磁気結合はトランス結合ではないものもあるようです。 >>416

ぼーぼーに毛が生えてますね!

>>394はそのタイプしか知らなかったのかもしれませんね。

実際はどうだったのか、>>394の話を聞きたいところです。 >>415

> 「絶縁できるトランス」とは「コイルが2つ以上あるもの」を指す

意味不明

その2つのコイルを磁気結合したのがトランス、コイルを2つ置けばトランスになる訳ではない。

> トランス結合ではないもの

トランス結合?

勝手に新語を作るなってw >>420

たぶん、「うんうん、そうだね」って言っとくのが吉な人だと思う 一点だけ

トランス結合というのは新語ではない

広くかどうかは知らんが使われている >>420

トランス結合は言葉としては使いますよ。

>意味不明

>その2つのコイルを磁気結合したのがトランス、コイルを2つ置けばトランスになる訳ではない。

本当に意味不明なんですか?

話を混乱させるために、当然の前提として存在することをないことにしてグダグダ言ってるだけなんじゃないのですか?

俺が

>「絶縁できるトランス」とは「コイルが2つ以上あるもの」

と言ったわけですが、互いに結合もせずに何キロメートルも離れた場所に置いた2つのコイルを想定しうるとでも思っているのですか?

これ、デジタルアイソレータの文脈での話ですよ? 結合が前提になってることぐらいわかりませんか?

で、トランスの2つのコイルの磁気結合によらない、磁気結合タイプのデジタルアイソレータがあるんだな、というのが >>415 の主旨ですよ。

>トランスと磁気って同じ

って書いている人がいましたので。

絶縁できないトランスならコイルが1巻のものもありますが、絶縁できるトランスなら、結合はしているけれど直流的につながっていない2巻以上のコイルが必要です。

コイルがあってもそれが1巻だけなら、「トランスで絶縁している」とは言わないと思うのです。 >>423

めんどうな奴だな。

なら、そのトランス結合を説明してみ。

あるいはトランス結合と磁気結合の、それぞれの具体的なデバイスをここに挙げてみ。 >>424

名前を尋ねるならまず自らから名乗るべき。

説明を求めるなら、まず自らが説明をするべきですよ。 そのトランスではない磁気結合だと、入力側に電源が要らないのがいいですね。

たいていのデジタルアイソレータは入力側にも電源が要ります。

アナログデバイセズのDC-DC内蔵型を使えば「外部から見れば入力側に電源は要らない」にはなりますが。

コイルに流す電流は数mAは必要っぽいですが、

フォトカプラを使っていたところでスピードを上げたいというような用途にはいい感じに使えそう。 >>427

めんどうな奴。そのまま返すよ。

自からトランス結合だ磁気結合だと言い出したんだろ?

なら、自らそれを証明するのが道理。

まぁ、出来ないだろうな。それぞれ説明出来るデバイスなんて無いんだからw

負けを認められない奴かw トランス結合とは違う磁気結合ってのはICがあるぞ。大昔だが使ったことがある。

一寸いまおもいだせないが、、、かなり高速だったと記憶してる。100Mbpsくらい

でつかっていたような気がする。 トランスの要件として巻線(コイル)が使われている必要はないからな

磁気的に結合していてエネルギーを伝達する機能を有していればトランスかと メーカー名を忘れてしまったなー。カプラよりも小型で高速だったから便利になった

もんだと思っていたんだが、その会社は潰れたのだろうな。今探しても出てこない。 GMRの原理を利用したのがあるな

Magnetoresistive insulators for contactless signal transmission between two electrically

isolated parts of electrical circuits were first demonstrated in 1997 as an alternative to opto-isolators.

A Wheatstone bridge of four identical GMR devices is insensitive to a uniform magnetic field and

reacts only when the field directions are antiparallel in the neighboring arms of the bridge.

Such devices were reported in 2003 and may be used as rectifiers with a linear frequency response.[30]

IL260 110Mbps 絶縁6Kvrms だな。 >>432

リニアテクノロジーはトランスによる結合だったかと思います。

>>433

むう。>>408をみて、便利そうな製品があるのだと気づけたのに。(GMR)

DigikeyでもRSでも入手可能なようです。 >>430

磁気的結合のないトランスもありますよ。 >>435

ほう

それは一般的ですか?

ぜひ具体例が知りたいですね >>430の

>トランスの要件として巻線(コイル)が使われている必要はないからな

>磁気的に結合していてエネルギーを伝達する機能を有していればトランスかと

ここでの定義によれば、

・トランスは磁気的に結合して、エネルギーを伝達するものである。

・トランスの要件としてコイルが使われている必要はない。

ということです。

トランスの狭義と広義の間のどこかの閾値には、こういう境界もあるのだろうと思ったのですが、

「コイルを使わずに磁気的に結合して、エネルギーを伝達するもの」はあるのですか?

圧電素子で永久磁石を動かして、リードリレーを動かせば情報の伝達はできそうですが、

エネルギーの伝達は難しいかな。 >>412

具体的に説明できないんですね。

ま、その程度の事なんでしょうけど。 FPGAの話題とは離れてますので、俺からの質問は>>438で終わりにします。 >>440

おやおや、圧電トランスでお茶を濁し、負けを認めず逃走かいw 本意ではないですが、質問は受けますよ。

なんか人が書いていることを読まないんですね>>441。俺が書いていないことまで見えちゃうのはまずいですよ。

>圧電トランスでお茶を濁し

濁してません。 これはマル秘情報だが、3.3V系(というか2.5V系がメインの)のチップに

5Vを加えてる箇所がかなりあって、それでずっとデバッグしていたのだが全く異常

なしで使えていた。納品間際で気が付いて修正して納品したのだが、なんの問題もない。

実は最大定格3.6Vなんて言っていても本当は5Vでも使えるんじゃないか?

応答スピードなんかには影響がでるかもしれないが、大半の用途では5VでもおK。

ではなかろうか、なんて思ってみた。 型式がわからんので、確定した話にはならないのですが、

VCCIO=2.5Vでも3.3Vトレラントな製品であれば、上向きクランプダイオードが入っていないものかもしれません。

この場合、入力耐圧は酸化膜のサイズ(だったっけ)で決まってしまうため、高密度な製品ほど耐圧が低い傾向があるそうです。

で、この耐圧自体が「正確に何Vで壊れる」というようには作れないのでいくらかのマージンがあります。

5VがOKだったのもそのせいじゃないでしょうか。

それを大半の用途ではOKというには抵抗があります。 >>444

5Vで動くのと、5Vを保証するのとは雲泥の差。

そんな使われ方されて、その車やら手術台に乗りたいと思うの? これで、糞のようなアイソレータの話が無くなるのなら

それは、良いい事じゃないか 絶縁が要らない5Vまでのレベル変換だけならそれ用のICを追加すれば事足りることが殆どかと思います。

今の時代、5Vトレラントなプログラマブルロジックを探して選択することは、メリットが小さいことが多いんじゃないですかね。

アイソレータの話題は、そんなもの誰でも知ってるだろう、と思っていたら案外知らなさそうな人がいたり、

俺も昨日まで知らなかったタイプのものがあったりで、なかなか興味深いものでした。 もう一つ付け加えれば、トランス結合とは真空管アンプの増幅段間結合の事。

全く関係ない話w >>452

あなたが、別のところで同じことを言って、陰で笑われないようにするために。

http://www.analog.com/jp/education/landing-pages/003/faqs_digital_isolators.html#3-3

トランスベースの伝達方法は通常、トランス結合に最適なAC信号(Ethernetなど)を伴うアプリケーションに使用されます。

http://newscenter-jp.ti.com/2006-01-25-TI

高い信頼性を同時に提供するとともに、既存のトランス結合型アイソレータ製品と比較して

http://release.nikkei.co.jp/detail.cfm?relID=430956&;lindID=1

電気的に絶縁することによってグランド・ループを切断します。このトランス結合された絶縁境界は、最大2,500VRMS

http://cds.linear.com/docs/jp/datasheet/j42701fc.pdf

一般的なイーサネット・データは2本または4本の銅のより対線(通称CAT-5ケーブル)で接続し、グランド・ループを避けるために両端をトランス結合にします。 >>444

発熱してんじゃない?

2年後とかに壊れるパターンだね。 >>454

>>444さんは出荷前に修正されたようです。 >>455

出荷前にそんな大きな変更して大丈夫なもんかねぇ

うちだったら許されないわ >>457

製品の性質で変わるでしょうね。違う世界がある、ってことで納得できるかと。 >>453

トランス結合でググって、俺は正しいとな?

負けず嫌いだねぇw >>460

ずっとテストしてて問題なかった物を出荷直前で変更するって

どういう意味か理解してる? >>460-461 話が噛み合っていません。

>>444は、出荷直前にトラブルを発見して、修正して出荷した

>>457は、出荷直前に修正して出荷、は自分の仕事場ではありえない、と言った。

この場合、>>457の仕事場で取る選択肢は、

「出荷直前にトラブルを発見して修正を行ったら、出荷を延期する」

であると考えられます。

>>460はそうは考えなかったのでしょうね。

「出荷直前に修正して出荷することが許されないのだとしたら、出荷直前にトラブルを見つけたら、修正せずに出荷するのだろうか」

と解釈した上で「そんなの怖いだろう」と書いたようです。

でも、これは>>457の仕事場で取る選択肢ではなでしょうね… >>461 の会社では自分のところでテストしてて問題なければ出荷するんだな、きっと。 そもそも、そんな初歩的なミスをする奴が設計してる時点で駄目だわ まあ、問題点として考えられるのは以下の2つ

1. 納品先にちゃんと報告して了解を得た上で出荷直前に修正したのか

2. 修正による弊害確認はちゃんとされているのか 5Vトレラントに変換するばあい、LVC245が便利なんだが、電源3.3Vで5V系

をドライブするのは問題ないが、じゃあ5V電源が使えるんか使えないのかが微妙だ

よな。実際には5Vでも問題ないが、データシートは微妙な書き方がしてある。 >>467

>>444の内容を見ると、3.3Vのデバイスの入力ピンに5V系の信号を入れていた

ということだろう

そして、実際には動いてしまい発見できていなかった

3.3Vのデバイスの入力段が壊れていないのはおそらく入力段に通常入っている

クランプダイオード(寄生ダイオード含む)が3.3Vラインにクランプしてくれており、

それにより壊れずに動いていたという感じだろう

ただ実際にはストレスがかかっており設計的には確実にNG

で対策としてLVC245を5V系デバイスの出力と3.3V系デバイスの間に挿入

することを考えていると理解したが、LVC245を3.3Vで動かすのであれば

LVC245は5.5V入力トレランとなので、この使い方であれば問題ないだろう >469

そういう甘い使い方ではないよ。出力が5Vトレラントでも電源を5Vにしていいとは

書いてないからね。 >>470

まさか3.3Vデバイスを5V電源で使ってたってこと?

だったらもはや唖然とするレベル

壊れてないのは奇跡に等しいのと長期的に確実に故障を招く

あとは>>466に書いた内容について対応したかどうかだな

もしダマで修正して納品したのなら、3.3Vデバイスを5Vで使ってた

設計的なポカ以上の大失態であり、最も信頼を損ねる行為を行ったことになる > 出力が5Vトレラント

なんかね、5Vトレラントの意味を正しく理解していなさそうなんだが? >>465

全然別じゃ無い。入力レベルさえ合わせられない奴の設計で

他に問題が無いと考えるのは頭弱すぎ。

製品のテストよりも先に、設計者をテストして弾いて置くべき >>467

>電源3.3Vで5V系をドライブするのは問題ないが、

これがOKなのは、受ける5V系デバイスが

・TTL互換の入力レベルになっている

・VIHが、VCC×0.6のような、比較的珍しいものであるかという条件がつきますね。 C-MOSの出力について5Vトレラントというケースはなくはありません。

https://toshiba.semicon-storage.com/info/docget.jsp?did=12713

LCXとVCXは出力トレラント機能あり

https://www.xilinx.com/support/documentation/application_notes/xapp311.pdf

A 5V tolerant output structure in its most basic form includes

a switch which allows the n-well of the PMOS output driver to follow the output pin voltage

upwards.

だれかが、「5Vトレラント出力でググって」って言いそうですが、ググってわかることぐらいは

わかる方がいいですね。 >>472

出力の方は、5Vでプルアップされても壊れない

とでも理解しとけばよろし >>470のと同じような話かな。

http://www.onsemi.jp/PowerSolutions/document/74LVC541A-D.PDF

With 5 V−Tolerant Inputs and Outputs

コンプリメンタリ出力で、ハイインピーダンスになっている状態で、5Vがかかっても大丈夫です。 LCX245とかだと、入出力の方向切替とかメンドイから

74CB3T3245みたいなバススイッチ系にしとけと 最近初めてFPGA搭載基板の設計をやってるんだけど、カップリングコンデンサの匙加減が分からん

EP4CE40F29ってFPGAでVCCIOを全部3.3Vで使おうとしてるんだが、

PDNツールで見積もったら全系統合わせても9個しか置かないとか出てきた

VCCINTには10uFって結構デカイ容量のも使おうとしてるし…

昔の他人が作った接続図見ると0.1uFのを大量に置くようなのばっかりなんだが、

デバイスの特性が変わったのか設計トレンドが変わったのか、自分が検討違いのパラメーター入れてるのか… 他人の過去品でも実績あるならバラまくな。

ヨタかんばん方式では、そういう安定供給を目的としたコンデンサは根こそぎ削るんだろうけど。 >>475

3.3V出力でも2.5Vは余裕で出るだろ? >>482

受ける5V系デバイスが

・TTL互換の入力レベルになっている

に該当。 >>480

そういう場合って、結局のところパスコン減らすことによるコストメリットが

どのくらいあって、その要求してるのが誰かってことによる

普通は、FPGA使ってる基板でパスコン減らしてコスト削減とか考えるのは

あんまり意味ないし、後で追加するコスト考えると、(せいぜい)

多めに設計しといて、実装するかどうかは後から決められるようにするくらいかと どのレベルの設計者だろう。

(1)ICのVIH、VILを満たす必要がある。

(2)ICの入力素子のH/Lが切り替わるレベルならOKだと思ってる。

(3)C-MOSの閾値はなんだかんだと理屈をこねても要するにVDDとVSSの中点だ。

(1)以外だとアウトな仕事場が多いのではないかと思います。

でも(2)、(3)を支持する人だって、74HCU04を反転アンプとして使ったら電源電流がたくさん流れることはご存じだったり。 5V-CMOSのVIHは3.5Vだぞ

エビデンスだバリデーションだとか言うなら

3.5Vは満たさないとダメだぞ >471

デバイスの型名が書いてあるんだからさー。

LVC245はRecommendied Operating Condition Vcc 3.6V(MAX)

だがAbsolute Maximaum ratings VCC 6.5V

になってるから唖然とするほどでもない。w

Vi 5.5V

Vo Vcc

だから5V系でプルアップされている信号に接続する場合には電源を5Vにするのは

アリだろ。(推奨ではないがな。W)

FPGA(3.3V) −−LVC245−−−5V系(10Kプルアップ)

5VのVIHは記述なしだが、恐らく2Vくらいだろだから余裕だし、、

そんなにやばいってほどでもないだろ。

やっぱり5Vの石に変えた方がいいか? >>486

>OKじゃない時が知りたいのだが。

5VのC-MOSデバイスには入力タイプで大きくわけて2種類があります

(1)TTL互換入力

(2)C-MOS入力

(1)は、3.3V C-MOSで直接ドライブできます。

(2)は、VIH min(Hであることが保証される最低入力電圧)が VCC×0.7 のものが多く、

この場合は>>487さんが書いているように、3.5V以上の電圧でないといけません。

中にはVIHが VCC×0.6 のものもあり、これなら3V以上ですのでドライブOKかなって感じです。 >>488

C-MOSデバイスのVIHは、次の2つの条件を満たすものに設定されているはずです。

(1)入力のNch FETをONにできる。

(2)入力のPch FETをOFFにできる。

74LVC245は、3.3VだとVIHは2Vとなっています。単純に言えば、電源に5Vを使った場合でも、入力に2Vを与えれば、(1)は成立しそうです。

でも、Pch FETのゲートソースに -3V がかかります。

低電圧で使えるC-MOSのPchは低いゲート電圧でONしますので、ちょっと怖いかな。

2電源ためのブリッジ用デバイスを使う方が安心です。 >>490に補足です。

ONにできる、OFFにできる、は完全にONにできる、完全にOFFにできる、の意味ではありません。 >>488

いやないわ

Absolute Maximum Ratingをなんだと思っているのか >Absolute Maximum Ratingをなんだと思っているのか

読んで字のごとし。w

でも6.3Vだろ。5Vなら1.3Vも余裕がある。無茶苦茶余裕があるということだな。

>でも、Pch FETのゲートソースに -3V がかかります。

これは出力の話だろうか?

LVCの電源を5Vにするのだから、出力のPch側にー3Vなんてかからないようなきがする。

先ずLVCの構造がどうなってるのか? 出力はバイポーラなのかCMOSなのか?

多分CMOSのはず。

出力がON(0V)の時

PCHのゲートにー3VかかるとONできないからありえないな。

出力がOFF(5V)の時(つまり10プルアップを経由して5Vが出力にかかる)

このときPchソースゲート間は−5Vになるのでは?

>低電圧で使えるC-MOSのPchは低いゲート電圧でONしますので、ちょっと怖いかな。

これは出力の直前のVIH、VILがどうなってるかだよね。電源が5VならCMOSだから0,5vだと思う。

だから全く問題ないと思う。 アッ、ごめん。入力の話だったか。入力が誤動作しやすいってことかな。ありうるね。ちょっと見当してみる。 >>480

> VCCIOを全部3.3Vで

> 全系統合わせても9個しか置かないとか出てきた

VCCIOだけならありえるかも。

でも保険で、もっと増やしたほうがいいと思う。

> VCCINTには10uFって結構デカイ容量のも使おうとしてるし…

コアにはそれは普通 >>494

> 無茶苦茶余裕があるということだな。

あんたの辞書にはディレーティングって言葉は無いのか? >普通に74VHCT使えばいいだけでは?

張り替えるのは、次回もし壊れたら修理のときだな。

1.直ちに交換

2.1年以内に壊れたら、無償交換。

3.1年以上たって壊れたら、修理費を貰ってVHCTに交換

連続稼働運転していて1か月以上動いているので、多分3を選択するのが最も合理的だと

思う。 絶対最大定格と一口に言っても、

・それを一瞬でも超えると壊れてもしらないよ。(つまりそこまでは壊れない)

・一瞬といったって、1μ秒が一瞬だったり1m秒が一瞬だったり、いろいろで。

・絶対最大定格までは、ちゃんと動作するもの。

・絶対最大定格は、壊れる限界でしかなくて、それよりずっと下で性能が怪しくなるもの。

・絶対最大定格は、壊れる限界でしかなくて、それよりずっと下でも動作しなくなるもの。

・実は超えて使っても、使い方次第で全然OKなもの。

などといろいろですね。 >>500

推奨動作電圧範囲〜絶対最大定格の間は正常な動作が保証されないので、普通の設計者なら推奨動作電圧範囲を越えないように設計する >>501

正しくは

推奨動作電圧範囲上限〜絶対最大定格の間は正常な動作が保証されないので

だな

それ以降は同意 >>501-502

推奨動作電圧範囲の規定があるものはそうなりますね。 >>500

お得意の検索で、絶対最大定格をググれば? ID:19OQrHh9 みたいな人って実社会では、で結局あなたはどうしたいの?

って言われる人だよね >>503

反証可能性を担保するため動作電圧範囲の規定がないデバイスの例を提示してください メーカーに泣きついても自己責任でどうぞご自由にお使いくださいと

言われる。 >>504は >>500の考え方が苦手な人なのでしょうか。

どの数値も超えたらだめだ、と頑なになっちゃう人がいます。

>>506

たとえばトランジスタの多くにVCEに関して推奨動作電圧範囲の規定はありませんが、VCEの絶対最大定格の規定はありますね。

レギュレータも推奨動作電圧範囲の規定がないことが多いように思います。 >>508

あんたの頭には「品質保証」って言葉は無いの?

なんかねぇ〜、話を聞いてると15年前の台湾PCベンダーのエンジニアと会話しているみたいだよ。

(PCパーツ買って組立ると、壊れまくりの時代)w 雑に「品質補償」とか言う言葉で根拠もなしに、考えることもなしに安心していると、混在した品質の

扱いに関しては品質低下するんではないか?

グローバル化すると必然的に様々な品質が入ってくるので、無根拠に拒絶するのは無根拠に受け入れる

ことと同じで、ようするに品質の管理能力がないということ。それがこういう結果として如実に現れたのだろう。w はぁ?

日米半導体協定から30年、1ドル79円の円高ショックから20年。

グローバル化とか、今更そんな昔の話を持ち出して、何が言いたいん? >>509

>あんたの頭には「品質保証」って言葉は無いの?

具体的に>>508のどれを指して言っています?

>どの数値も超えたらだめだ、と頑なになっちゃう人がいます。

これでしょうか。

品質保証と矛盾しない絶対最大定格の項目もあるんですよ。

絶対最大定格そのものがちょっと曖昧なのが問題だと思うのですが。

>>509さんは「すべての部品のすべての絶対最大定格は一瞬たりともどの数値も超えたらだめだ」と考えておられますか? >>512

>「すべての部品のすべての絶対最大定格は一瞬たりともどの数値も超えたらだめだ」と考えておられますか?

>>509じゃないが答えは「はい」

設計者は公開されていないデバイスの「実力」をアテにしてはならない >>513

(1)Microchip社は、公開しているドキュメントにおいて、3.3Vで動作するデバイスの信号ピンを

5V で駆動する方法の一つとして、直列抵抗と、IC内部のクランプ抵抗を使う方法を示しています。

(2)一方でMicrochip社のマイコンでクランプダイオードを持つ入力ピンの絶対最大定格は、最大で VDD+0.3V のような規定になっています。

(3)そのすぐ近くに、クランプ電流の絶対最大定格として±20mA とあります。

では↓これはどのように解釈されますか?

(A) この場合(1)を実施すれば入力電圧はVDD+クランプダイオードのVFとなり、(2)の規定を上回ります。矛盾はありませんか?

(B) クランプ電流が流れる時点で(2)の規定を超えています。(3)の規定は無意味ですか?

絶対最大定格といえども、各項目には隠れた条件があります。それぞれを単独で考えるとますいですよ。 >>514に書き忘れました。

Microchip社を例にしましたが、探せば割とみつかります。 >>513

> 設計者は公開されていないデバイスの「実力」をアテにしてはならない

だねぇ

評価したデバイスが、たまたま出来が良かったかもしれない。

評価した環境が、たまたま好条件に振れてたかもしれない。

生産工場の変更により、特性が変わるかもしれない。

そんなアテにならないので設計したら… > 探せば割とみつかります。

探して見つかったら俺の勝ち論法、それが誤情報であってもw とにかくググってググってググりまくって自分の正当性が崩れないように必死な人だな

実社会でもそんな調子なんだろうな

おつかれさま

ID:pJJDaZ/+ >>514

俺なら、その(1)と(2)の矛盾をまずMicrochipに問い合わせて、

(1)を保証するというのなら(2)の絶対最大定格をVDD+マイコン内部の

クランプダイオードのVFの値に書き変えさせる

それができないなら(1)を取り下げさせる

という行動をとる ここでの話って勝ち負けなのかな。

「例外がある」という提示なので、もし勝ち負けに拘るなら、提示した例外が間違いであることを証明すればいいと思う。

勝ち負けじゃなくて技術の話をすればいいのに。

クランプダイオードによる5V入力対応と絶対最大定格と推奨電圧の関係はメーカーで思想が違っていて面白いところですよ。 >>519

それもひとつの考え方ですね。実際それに近い表示のメーカーもあります。

ところが、そのVFがばらついたり変化したりで一定ではないものだから、低インピーダンスの電圧源で駆動したときに

壊れないことを保証する電圧としての最大電圧ではなくなってきます。

多くのメーカーで、上向きダイオードを備えた入力の絶対最大定格がVCC+0.3Vとか、VCC+0.5Vのように

ちょっとVFより低めに設定されているのは、低インピーダンスの電圧源で駆動してもどかーんと電流が

流れないことを保証するためです。

・絶対最大定格は絶対である ← ふふふ。

・絶対最大定格には条件により例外的解釈も必要だ ← (俺) ← ありえない(>>517 >>518)

・絶対最大定格には矛盾がある場合がある ← >>519 >>521

当然VDD+VFの規定はVFのばらつきまで考慮して設定してもらう

とまあそう書いた訳だが、つまるところ、そこまでしてギリギリを

攻めるような設計は実際にはせず、あくまで動作電圧範囲内で

動作するよう設計し、絶対最大定格はデバイスメーカー側の

マージンとして取っておく

あなたが何と言おうがこれが私の設計ポリシーなので

これ以上言うことはありません Virtex-5が載ってる基板のタンタルコンデンサの置換を考えてるんだけど、どうしようかと迷ってる

現状VCCINTに220uF*4(推奨値は330uF*2)、VCCAUXは33uF*2(推奨値とおり)だけど、

単純に同容量程度のMLCCに置き換えで良いのか…?

一般に容量は若干小さくできると思ってるんだけど、UG203のTable 2-11の注記の

"2. ESR must be within the specified range."って記述が気掛かりだ

現状基板の電源ノイズ測定はできる状態じゃないし、参ったわ… >>523

> "2. ESR must be within the specified range."って記述が気掛かり

俺なら守る。

タンタルはセラコンよりESRが高い分、ある種のスナバになるんじゃなかったっけ(うろ覚え)

それにしてもセラコンにしたら、高くなるんじゃね? タンタルが嫌われる(避けられる)理由はありますが、最近のものはずいぶん改良されているはずです。

セラコンも

値段が高くなる、ESRが低くなりすぎ、規定の静電容量が必要な場合は大幅なマージンを見ないといけない、

適当に選んだり実装に配慮がたりないと短絡する、

といった心配もありますし。 >>524,>>525

タンタルの廃止は絶対条件でして、、、

ESR低すぎると発振するんだっけ?(電源モジュール直後に置いたときの話?) >>529

タンタル禁止かぁ

予算はあるの?あるならAW屋さんにプレーン共振シミュを依頼。

無いなら自分でモデル作ってLTspiceでタンタルと比較。

でどぉ?エイヤで基板作ってしまう手もあるけど。 タリウム…

>>529

タンタルの廃止は絶対条件でして、、、

ああ。やっぱりルールですか。自分で良しあしの判断をすることが許されていないわけですね。

いくら改良されても、紛争鉱物のレッテルは外れそうにないみたいですし。 自分は誰よりもよく知っていないといけないという強迫観念 >>535

産出国がね・・・

紛争鉱物ってやつだ。 おい、ありそうでない、オーディオ帯域の6桁周波数カウンターつくらないか?

入力オーディオ信号を淫売太ででデジタル化したあと16〜8192分周してその周期を100MHz位の

クロックで計測して、マイコンで周波数を計算する構成が。

昔はそんなカウンターICゴロゴロあったように思うのだが見つからない。

24ビットの同期カウンターで SPI出力 FPGAなら簡単なんだろ?

たのむぜぃ 国が内紛状態で、反政府武装組織がタンタルを資金源にしてて、って聞くと、コンゴの人大変だ、って思う。

でもコンゴの政府軍がウガンダとかルワンダと交戦したりルワンダが反政府軍を支援したりと憂鬱な展開。

とりあえずタンタルコンデンサを沢山使ったら、それがサードパーティが勝手に作ったカラシニコフに化けるのだと早合点しておく。 タンタル禁止はそういう理由ではないとエスパーしてみる 単たる禁止は単たるの故障モードが短絡で結果発火するから だよね

それを紛争鉱物とか、なに言っちゃてくれてるの あるるんだって異臭発煙しますやん。

萌えたのはまだ見たことないけど。 社内ルールにおいてタンタル禁止の理由が短絡故障なのだとしたら、大容量セラコンも要注意。

機械的ストレスに気を付けて、かつ、短絡故障をおこしにくいように作られたセラコンを選んでリスクを下げるわけだけど、

たまに「セラコンはタンタルみたいに短絡しない(キリッ」って感じの人がいて怖い。 コンデンサ自体トラブルを引き起こしやすいから大容量を期待していない >>746

>コンデンサ自体トラブルを引き起こしやすいから大容量を期待していない

でもこの話の発端は 330uF×2 のタンタルをセラコンで置き換える、って話ですよ。 デリバリで、痛い目にあったんだろ

良くある話だ

この手のトラブルは、規模の小さい業者ほどダメージがデカイからな

どうにもならない

例え5円の部品でも、入手できなきゃ製品そのものが止まる >デリバリで、痛い目にあったんだろ

ああ。

俺はMaximを使うって言ったら購買に睨まれたことが。 >>545

> たまに「セラコンはタンタルみたいに短絡しない(キリッ」って感じの人がいて怖い。

たまに「絶対最大定格まで使っていい(キリッ」って感じの人がいて怖い。 >>550

ははは。もしかして上向きダイオードでクランプされた3.3Vロジックで5V入力を受ける際に、

絶対最大定格や、推奨電圧範囲を超えることについて根に持ってるの? タンタルとセラミックに関しては、俺も実は「セラミックは短絡故障しない」と20年ぐらい前まではなんとなくそんなふうに思っていました。

会社の設計指針でもタンタルは信号ラインでしか使ってはダメとか、直列に**の抵抗を入れろ、とかあるのに、セラミックに間しては

そういうことは書かれてなかったし。

タンタルの短絡故障のもうひとつの問題点は発煙と臭いだろうなあ。

セラミックが短絡したとき、セラミックコンデンサ自体は静かに発熱する。これで助かるかどうかは電源次第だけど。 >>549

試作で10個欲しいって言ったら営業さんから「サンプルで送りますから」って言われたよ。マキシム。 >>554

そうなんよ。サンプル無料って昔から気前が良かったんだけどな。

いざ製造ってときになると、最低発注個数がとか、製造のスケジュールでそのチップの次回供給は来年の○月だとか

みたいなトラブルに購買さんは悩まされてたらしい。(MAX232のようなポピュラーなのは別だけど)

今はそういう話は聞かなくなったように思う。いろいろ改善されたのかな。 今や、「購買・資材部門は不要、そいつらに払う給料で初回製造時に

将来生産分の部品一括購入しとけば、デリバリーの心配は無用」って

極論なんだろうか?(税務処理の点も含めて) >>557

いや、それ以前にMaximを選ぶところがアホなんじゃないか? >>557

購買・資材部門は不要とは思わないけれど、一括購入で解決できると思うことはときどきある。

保管の問題はあるんだが。 電機部品はやすいからな。でも2度と使わないような部品を大量に買うのはばかげてる

から、そういうところは設計者でないと勘が働かない。 昔は、1ロット〇個使いで年〇ロットくらいって言っといたら

適当に数まとめて発注・在庫してくれる部品商社もあったんだけど

今の時代そういうのは無理なのかな? どこもかしこも

倉庫持つの嫌

倉庫に入ってる部品の品質を管理するの嫌

だから

在庫持つの嫌

時間指定で納入しておくれ

ってな訳で なんの話をしてんだか。

経験則で言えば、部品種数で8割は他の基板と共通化出来る。 随分とスレ違いな流れだけど

ICをストックしときたいが

・保管・管理の手間かけたくない

・ストック品が高く売れるなら売って小遣い稼ぎしたい

そういうときは、Chip1Stop ・・・ じゃなかったっけ? TD4ってXC9536に余裕で入るらしい

作ってみようかな >>567

トラ技の付録のMAX2でも6割くらいで収まったと思う ・XC9536に余裕で入るらしい

・MAX2でも6割くらいで収まった

全然話が一致していないw なんでタンタルなんだろ

ニチコンの電解コンデンサ四隅においとけ >>480

ああ、6端子ぐらいに0,1uFいれておけばOKとかそんな感じだから

安さと波長の関係 >>573

そんなに売れる製品でもないし、一回買えばずっと使えるし、しょ〜がないべ。

基板製作直後にザザッと全信号を見れるから、重宝してる。 >>574

レスどうもです

確かに一度買えばずっと使えますね

USB-JTAGのインターフェースつきの奴買ったほうがいいのかな…

どのUSB-JTAGでも基本的に使える感じなんでしょうか? トラ技の付録とか、もう10年以上前なんだな。

またそれなりの規模のCPLD/FPGAが付録になってくれないかな Vitex Ultrascale+ 基板付き 300万円!

でも LED チカチカしか出来ない基板クオリティー メモリをどどんと4Gとか8G積んでるなら仮想通貨マイニングとかやる人出そうだけどw 古い話で恐縮ですが、ご存じの方いらしたら、教えてください。

Xilinx ISE14.7で、以前のソースを改造して使おう、というとき、

以下の手順で操作したのですが、 >>580さん補足早く!

つまらないことでスレがギスギスしてきた >>585

それだと「イカゲソ」食べられないでゲソ 最近IntelCPUはAMDにちょっとシェアとられてるらしいから

空いたラインをこっちに回してくれたりしないかな? 論理合成でシノプシスのsynplify使っている人いる? >>590

synplifyでxilinxのVIOてインプリ出来る? ISE よりはずいぶんよかった。

Virtex5 でLEを90%以上使っても諦めずに合成してくれた。

Vivado になってからは知らねえ。

ってか、まだあるんだな、simplify パソコンから画像データ転送してFPGAで画像処理させたいのですが、ボードは何を買えばいいのでしょうか >>595

でなにがいいのよ

Python使えて嬉しいことについて >>595

なるほど

alteraボードでのおすすめはありますか? こんにちは。latticeのxp2で5V入力扱いたいんですが、

xilinxのナレッジにあるような、内部の保護ダイオードに

頼って直列抵抗で済ますというのは可能でしょうか?

lattice xp2のデータシート見たんですが、保護ダイオードが

入ってそうな記述をみつけられませんでした。 >>597≠>598?

文>>594からいきなりVerilog覚えろは厳しそうって判断したんじゃないの?>>595は

入口としてPYNQはありよ

一般価格でもXのとしては安いし 画像処理ったって何をしたいのか分からんし、

PCIe でリアルタイム転送なのか、USB でいいのか、XMODEM でたらたらでいいのか。

予算も何も書かずに「何を買えばいいのか」なんて、小学生かよ。社会人としてどうなの? PYNQは小学生には無理じゃないかな

購入ページが英語だし(まあ大人が購入すればいいか)

スタートガイドやサンプルも英語だし(まあ大人が教えてみせればいいか)

Webブラウザで操作できるけど基本Linuxだし(まあ大人が教えればいいか)

まあどうにかなるか ただFPGAって入門向けの情報がまだまだ少ない気がするよね 10年後にはC言語と同じくらいFPGAの入門書も書店に並んでるんじゃないかな(楽観的) Intelがすんごい需要作ってくれるはず

(楽観的) IntelほんとなんでAltera買ったんだろうね サーバのアクセラレータ需要を見込んで買ったのかと思ったら車載に進出とか言ってるし

なんか迷走してる感ある XeonとFPGAを組み合わせて、カスタムできるCPUにしようとかなんとか で 、 P Y N Q だ と な に が い い ん だ よ Academic $65 だけだな

それ以外は、 競合より劣るスペックのくせに 値段は高い

やる気ねぇだろ ただFab埋められる需要が欲しかっただけなんじゃ?

それだけでAlteraごと買っちゃえ!になるのもw Xeon+FPGAって使い物になるのかな

サーバ用途だが、プログラマーもFPGA屋も使いこなすのは難しそう

MicrosoftやGoogleのハイスペックエンジニアくらいしか使えなさそう >>615

alteraだと性能よくて安いボードあるの?

素人なんだけどarty z7-20買おうか悩んでたとこ。 >>614

簡単にSSHでログインできてLinuxの操作ができるので、FPGAの理屈がわからずビットストリームも生成できないような素人でも簡単に動作確認できて劣化ラズパイ的な使い方ができる Quartus2 Standard Editionの30日ライセンスが切れてもう30日使いたいんだけど

だれか裏技おしえてください。 上位2社が見向きもしない小規模用デバイスっていまどこが主流ですか? >>624

そ〜言うのはLattice使っとけ

serdesが速けりゃもっと応用ふえるのにとは思うが >>624

俺もLatticeは便利に使ってます。

でも、俺個人はIntel Alteraから離れているのですが、MAXシリーズには小規模デバイスがあって

いまでもアクティブなんじゃないのですか?

Xilinxは開発ツールからして、過去のものにしたがっている様子ですけど。 >>624

主流は知らないが、Maxとか旧Cycloneかな。

理由は、ツールが変わるとメンドイから。

探すと、LE単価が旧シリーズが安かったりするし。 >>606 ディジタルフィルタの実装で使う用途が多いから、FPGAの雑誌は

FPGAそのものというより、フィルタ理論がわかってて当然という雰囲気があるから

マイコン雑誌より要求レベルがあがるね。 >>628

matlabかscilbでフィルター係数出して入れるだけやん ALTERAのDE0というFPGAを買いました。

40ピンの外部I/Oコネクタがあります。FPGAのピンからそのまま直接出ているようです。

FPGA回路図を見ると、

VCCIOに3.3V、VCCAUXに2.5V、VCCINTに1.2Vが接続されています。

FPGAに信号を接続したいのですが、FPGAに5Vがつながっていないので、

5Vの信号を入れても大丈夫でしょうか?

瞬間なら大丈夫で、連続だと抵抗をかませば大丈夫、とかありますでしょうか? >>635

5V信号をそのままはI/Oに挿すのはNG

必ず抵抗か何か使って3.3Vに降圧すること 抵抗入れても5V TTL出力を入れるのはちょっと憚られる >>635

いろいろな考え方があるかと思います。

(1)ダメ

(2)デバイスのアプリケーションノートに掲載されていれば良いとする。

(3)上方向のクランプダイオードの規格を満たせばOKとする。

心配だったら抵抗2個で分圧すればよろしいのでは。 http://www.altera.co.jp/literature/an/an447_j.pdf

この辺りを見ると、一般論に留まらずクドクド書いてるから 実際にも弱いと思えるな

これ絡みで、過去にトラブルでも起こしてるのかも?

甘く見ない方がいいぞ >>642

詳しく見てないですが、

・LCD側がTTL互換レベル入力。

・リードを想定していない。

ってことでしょうか。

LCDの内蔵ドライバの駆動力ってたいしたことがないものが多いので、

仮にリードしても、直列抵抗&クランプで逃げられる、という発想でしょうか。思い切ったな。 LCD からリードするのって ready になったかどうかくらいだし

タイマー使えばそれも要らないしね。 >>635です。

みなさん、アドバイスありがとうございました。

やっぱり3.3Vまでしかだめみたいですね。データーシートを探し出して見てみたら

VCCIO=3.3Vなので、3.3Vが最大でした。

GPIOコネクタは40ピンで2つあり、1つのほうにはダイオードが縦に入っていますが

もう一つは入っていません。FPGAの足そのものを外部にズルズルと

引き回すのは怖いですが大丈夫なのか謎です。

LCDは4.3Vで動いています。FPGAへは120Ωの直列抵抗を入れて4.3Vを喰わせています。

電源関係はこんな感じです。

ACアダプタ7.5V→フルブリッジ整流ダイオードで逆接防止

→3端子レギュレーターで5.0V、これをVCC50と呼ぶ。

VCC50→3端子レギュレータ→3.3V、2.5V、1.2V

VCC50→トランジスタをダイオード代わりにして 4.3V→VCC43

VCC43→LCD電源

LCD→120Ω→ダイオード縦→FPGAのピン 実はDE0のPS/2端子は5VがそのままFPGAに入る設計 >>646

PS/2はホスト側でプルアップして、駆動はホスト、デバイスともオープンコレクタじゃなかったっけ。

もしそうなら、デバイス(キーボード、マウス)の電源は5Vであっても、DE0で3.3Vでプルアップされていれば

問題にはならない気がします。 あれ、回路図見直したらちゃんと抵抗とクランプダイオードで3.3Vになってる。 >>647

回路図を見るかぎり、FPGAの前に直列抵抗(120Ω) & クランパ(BAT54SW)の構成で保護されてる

>5VがそそのままFPGAに入る設計 ってのは嘘だね

DE0:PS/2 のプルアップは対5.0Vで2kΩ、上の外部保護回路を通した後に FPGAに接続 GPIOコネクタ(40pin)が2つあるけど、ダイオードが入っているのは片方だけですね。

何ででしょうか? コストダウンじゃ?CVも回路図には両コネクタともダイオードが書かれてるが、実装されてるのは片側のみ http://www.itmedia.co.jp/pcuser/articles/1708/29/news100.html

(MS)スライドの説明文

>FPGA内のSoft DPUのアーキテクチャ。Cライクなプログラミングモデルを採用しており、FPGAで一般的なHDLやRTLの記述手法とは異なる

約20年いろんなとこが挑んでは散っていったけど

今度のは使い物になる性能出るんかね? 今更Cかよ。

Python とか Haskell とかあるだろ。

オレは書けないけど。 >>655

Cとアセンブラの関係と同じで、職人がゴリゴリと書いたコードには勝てないよ。

ただ、その出来たFPGAのAIがゴリゴリする様になれば…w ソフトウェア言語は基本的に逐次実行だから

FPGAの性能を引き出せないんだよね

MSならせめてasync-awaitあるC#ライクなの持ってくりゃいいのに >>658

「ソフトウェア言語」で一括りするなよw

知らないと思うが、VHDLの元のAdaは並列処理言語だぜw 知恵を忘れたらFPGAという深い沼から己が抜け出せなくなるであろう

いつの時代になっても、言語という枠に囚われてしまう方出るのは、イイネ! >VHDLの元のAdaは並列処理言語だぜw

AHDLじゃないのでしょうか? Cだろうがほかの言語であろうが、

結局は表記方法がそうなるだけで、

記述する内容はそこまで大きく変わりそうにない気がする。

VerilogとVHDLの違いと同レベルになるかなと。

大事なのはハード記述方法の概念的なもので、

言語(表記方法)は何ライクでも特には気にしないかな。

ただCライクだったりすると、

統合環境等を流用しやすかったり、

いろいろな補助ツールも利用できたり等、

そういう面ではいいこともあるかな。 ソフトウェア言語なんて聞いたことないが、

つまりはハードウェア記述言語としての対比ということで、

VHDLは含まないということだろう。 AHDLってAlteraHDLだよね。

VHDLよりはハードウェアに近い感じの記述をしてたような、それでいて、ABELやPALASMに比べればずっとわかりやすかったような印象。 ABEL AHDLの方がずっと先(少なくともPCレベルに降りて来るのは) 使い分ける程頭が良くありませんとか素直に書いたら? >>670

いや、しかし既存のハード記述言語は、糞過ぎる。

もう少しハード向きの言語を考えた方がいい。

VHDLもCもFPGA向きじゃない。

Cでハード記述なんて、COBOLでOS書くくらい場違い。 >>675

どういうのがFPGA向き言語か提示して下さい VerilogにしてもVHDLにしても、論理合成は後付けって事を考えたら、よく出来てる。

>675 が「糞すぎる」ってんならそれを超える物を見て見たいです。 自分には合わない、ということが分からない人は少ないですが、

自分に合うものを作ることができる人は少なくて、

割と多くの人に会うものを作ることができる人は限られてしまいます。

自分に作れないものを批判することを、恥ずかしいことだと考える人と、岡目八目だと考える人がいます。

でも後者のほとんどは自分視点でしかなかったりして。 シーハテハテ

論理合成に最適化した回路記述言語。Cと付いているが、全く似ていない。 AHDLの方が遥かにましだったが、なぜか消えたな。 昔はMAX5000のころはさら有料のツールのほかにに別に金が必要だったからAHDL+回路図入力でやってたな。 言うて半導体だからなぁ

300MHzレベルとかだとタイミングエラーすぐ出るし、遅延考慮のレジスタスライスとか考えたらRTLじゃないとキツイ >>677

ソフト言語でFORTRANやASMを蹴散らして、Cが栄えたのは、

文法エラーが無ければ、基本的に構造化構文になってメンテナンス性も移植性も高いから。

ハード記述言語も同期回路以外は、

文法エラーで記述できないような言語仕様でないと、

メンテナンス性も移植性も悪すぎる。 >>686

最初に読んで俺もそう思ったが、半分は正しいかもよ。

> メンテナンス性も移植性も高いから。

それまでアセンブラで書かれていたOSがCで書かれるようになり、メンテナンス性に移植性が向上したのは事実。

そのお陰でUNIXが普及したしね。

> ハード記述言語も同期回路以外は、文法エラーで記述できないような

これは間違い。

VHDLは、その気になれば基板の設計も出来る。当然、アナログ回路とか電源も含まれる。

FPGAも同じで、非同期回路が書けないとこまってしまう。 UNIXがまともに普及したと言えるのはOSXから。 VHDL

- 設計仕様のドキュメント言語として開発

- 読解性に優れ、システム仕様の曖昧さを排除した厳格な言語

Verilog-HDL

- C 言語を基にし、ASIC 設計の記述性を重視した言語

- ゲートレベル・シミュレーションの為の機能も充実

これって本当か? どうしても必要な1%の回路にも非同期回路が使えないような

言語では困ってしまう。 非同期回路って本質的ではないように思う。現実的には同期的にしかシミュレーションできない。 >VHDLは、その気になれば基板の設計も出来る。当然、アナログ回路とか電源も含まれる。

その気になればといわれても、意味がわからない。Net配線ができるだけってことなら

別に言語つわかなくてもできるんだから意味がない。当然アナログの動作シミュレーションが

できるということでなくてはならないと思うが、、、出来るんだろうか?

無理やりこじつければできないことはないだろうが、それならCでも,exelでもできる。 仕様書を理解して言語を書かないでMOS回路で全て組めばいいんだよ!!!w >>691

お前さんのやっすいシミュレータではそうなんだよな? VHDLで入力ピンマトリクスでのビンゴゲームを書けますか? >>690

1%も非同期な回路があってちゃんと実装できるか?

昔のPLDなら、問題なかったかもしれないが、FPGAと呼ばれるデバイスで

1%も非同期な動作してたら、まともに動かない以前に、

リソース不足とかでビルドが通らないと思うが。 >>698

なんか勘違いしてるみたいだが、論理式はすべて非同期回路だぞ >>699

何か勘違いしてるんじゃないかと思うがマクロセルを使って非同期回路を作るって意味だろ。 言葉尻しか捉えられない連中の事はほっといていいのではないでしょうか。 >>697

DAとオペアンプつないで「ビンゴ」とかしゃべらせるのは工業高校ですらできるよん まあいろいろ問題はあるにせよVHDLやVerilogは諦めて、もうすこし抽象度の高いところで、マシな言語を考えた方がマシ。

でもそうなると手法レベルが必要なのであって言語はC#でもJavaでも優れた言語あるのでそれを使えばいい。 システムcの抽象化ってどうよ。チャンネルってのが気になる。というか気に障る。普通に接続だけでよかったような

気がする。 > C#でもJavaでも優れた言語・・・

確かに初心者向けに垣根を下げる効果はあった

しかし結果はどうだった?、ポエム・レベルの糞アプリだらけだったろ

初心者歓迎ってわけじゃないからな

金も時間もかかる、習得できなきゃ諦めろ

そういう事だ CとかはCPUの命令セットを生成する言語だから演算、分岐、代入などがしやすい文法になってんでしょ?

HDLだって論理ゲートやFFの構成を記述しやすい文法になるのが普通で、Cに似せるなんて無理があると思うよ。 プログラマ連れてくればハードも作れるよって発想がそもそもアホ。 >ポエム・レベルの糞アプリだらけだったろ

つまらない主観 >>705

いや、もっと抽象度の低い言語が必要。

もちろん将来的には、抽象度の高い言語に進むだろうが、

抽象度の低い言語がグダグダな段階で、

抽象度の高い言語を開発しても、実用的なものが作れない。 >>714

じゃあ、回路図入力だな

頑張ってくれ

ネットリスト入力もあるけどね >>708

> Cとか 〜 演算、分岐、代入などがしやすい文法

演算・分岐・代入なら、事務処理言語COBOLでも、科学技術計算言語Fortranでも出来ること。

Cは、格好よく言えばシステム記述言語。そこがそれまでの言語と決定的に違う。悪く言えば高級アセンブラw

> HDLだって論理ゲートやFFの構成を記述しやすい文法

それだけなら論理式で今でも出来るやん

> Cに似せるなんて無理があると思うよ。

なぜCはシステム記述言語と言われるか?

それは強力なビット演算にメモリアクセス、それにレジスタのビット幅に依存しない言語仕様だから。

そう、HDLと比較的親和性は高い。

ちなみにVHDLの元になったAdaは、Cよりさらに高級なシステム記述言語だったりする。 ついでに言えばAdaはCにも影響を与え、ANSI-Cを産み出した。 adaがひどすぎるのでCが生まれる切っ掛けになったという意味では影響にはちがいない。

ではあるが、影響っていう言葉は一寸使い方が違う気がする。影響の正しい使い方として

文字通りに影響を受けたのはVHDLだろう。

hello.adb

with Ada.Text_IO; --文字列の入出力のために必要なライブラリ

use Ada.Text_IO; --Putを直接呼べる

procedure Hello is --プロシージャ。名前はファイル名と一致させる。ただし大文字開始

begin --Helloプロシージャ開始

Put("Hello, world!"); --文字列出力

end Hello; --Helloプロシージャ終了 >>714

開発は不思議なものでどんなに綺麗なベースを作っても、グダグダにする人が現れてそれを引き継いでグダグダにする。

言語もそれに似ている。

AHDLは非常にきれいな言語だが完成したものの9割はグダグダだ。Cも非常に綺麗な言語だが完成したものの8割は

グダグダだ。

大局的見地からすれば諦めるということが最も賢明な選択だろう。

アーティストといわれる人は道で拾ったガラクタを組み合わせて美しいアートを作り上げる。VHDLでも美しく作ることが

できないことはない。 非同期リセットの検証は、アサーションでがちがちに固める以外になにかあるの? >>718

> adaがひどすぎるのでCが生まれる切っ掛け

誰がそんな事を言ったw

誕生の順番なら K&R C → Ada → ANSI-Cだよ。

最初のCが酷かったので、Adaの良いところを取り込んで改良されたんだよ。今のCのキャストもAdaの影響。 >721

時代は常に孕んでいる。adaができるにはその原因はずっと以前からある。そして伝統は

否応なしに受け継がれる。窮屈でも不自由でも諦めて使う以外にない。 >>722

Ada以前を語れってか?

面倒くせ〜し、流石にスレチだわ

要点は、Cはシステム記述言語であり、資産もあり、書ける人も多く、

最善策ではないが次善策としては高位合成に適した言語だって事。 Cを拡張して新しいHDLでも作りたいの?Velilogで十分だと思うけど。 >>723

全然適してないって。

本当に設計したことある? 本当にverilogやVHDLより圧倒的にいいと思うんなら仕様だけでも公開したら。

有志が実装してくれるかもしれないし。 System Verilog もさ、logic とか取り入れて抽象化したいのかと思えば

always_ff や always_com って思いっきりレジスタ意識させてるし

意味分からないよ。 >>727

背景を知らないとそう思うだろうな。

Sysuem Verilogはあるのに、なぜSysuem VHDLは無いのか?

答え、Sysuem Verilogで拡張部分は元々VHDLは持っていたから。 >>727

SystemVerilogは抽象化寄りじゃなくて記述量とミス削減目指してるんじゃない? 20年前にWindowsを中心に開発環境が激変したからなぁ。

キ-ワードの色は変わるわ、リアルタイムで文法チェックしてくれるわ、

タブの位置、整形までしてくれて、インテリセンスまである。

変数にマウスを当てれば型を教えてくれ、関数をダブルクリックしたら定義に飛んでくれる。

これは言語のあり方まで変えるほどのインパクト。 >>723

全然適してないと思うよ。

ハードの記述には、少なくとも、オブジェクト指向の概念は必要じゃないかと思う。 解かってそうなのは、>>729 ぐらい

後は、バカばっか >>728

なんで、そんなに必死にSysuemってするんだ?

お前らはSystem Verilogを使っている? >>733

教育関係者だけど、初心者にはSystemVerilogの方が良さそうなんで、

使おうとしてるところ。

今わかってる唯一の難点は、default_nettypeをnoneにすると、

input logic使ったらModelSimがエラーになること。Quartusは通る。

せっかくlogicで統一できるかと思ったのにな。 初心者には辛いだろうな。VHDLもVerilogも巧みに本質を外すから。料理を習いに来たのに皿洗いを3年間やらされる

感じだろうな。 後はバカばっかなんだって。天才すぎて大変そうだね。バカにも分かるように説明してあげなよ。 logic じゃなくて bool がいいのに。

uint13 なんかも欲しいな。 非同期リセットの検証は、アサーションでがちがちに固める以外になにかあるの? >非同期リセットの検証は、アサーションでがちがちに固める以外になにかあるの?

アサーションを大量に入れるのは無意味だろう。非同期なので無限に必要になる。

大量に入れるのではなくて、大量に検証を行うのが正しい。あらゆる非同期のすべてのタイミングを検証する。

それ以外には方法はない。 >>741

お金出せばツールで出来るとかウソだったのね!ひどいわw

ありがとう XilinxのSpartan6-LX9で教えてください。

LVCMOS33 を、8本

LVDS25 を、2本

を取り出そうと、FPGAの足から線を取り出し、ピン割り付けをしたらエラーになりました。

LVDSとLVCMOS33は、同じバンクでは取れないようです。

別のバンクに変えたら、ちゃんと動きました。

たった2本のLVDSのために、1つのバンクが全部LVDSになって、

LVCMOSは使えなくなってしまうのでしょうか?

もったいない気がします。 バンクを小さくすればいいのだが、そうすると別の問題が出る。 バスで「ウチの前で止まってくれないかなー」って叫んでるようにしか読めないけど

嫌ならASICでも作って、って話。 ピンが足りないってことかな?

おっきなパッケージ使えばいいじゃない。 IOバンクってのはIO電圧を複数使えるようにするためなんだが

この場合、バンクの全部がLVDSになるのではない

バンクの全部のIO電圧が2.5Vになる

LVCMOS25なら使える

っていうか、この程度を資料から読みとれないレベルでLVDSなんて使えるのかね >>74

LVCMOS33を使いたいって言ってるから、LVCMOS25ではないよ。

電圧足りないじゃん。 これこれ「なら」使えるという条件提示に対して、そうじゃないとかいう言わずもがなの指摘をする心理がわからん >>748

言葉のアヤみたいなところにつっこんでも荒れるだけです。

テクニカルな部分で意思疎通ができてれば良いのですが。

元質問は

>たった2本のLVDSのために、1つのバンクが全部LVDSになって、

>LVCMOSは使えなくなってしまうのでしょうか?

となっていて、バンク全体がLVDSになるのではないかと心配しています。

それに対して、>>747は

・全体がLVDSにならない。

・バンクごとに電圧が変わるだけ。

・LVDSが使えるようにしたバンクでもLVCMOS25なら使える

と適切な解説をしているように見えます。 さまざまなI/Oを使えるようにしているから、

使うI/Oの種類によってI/O電源かえる必要がある。

これはFPGAに限らずASICだって何だって一緒。

(レギュレータ内蔵しているようなものなら単電源もあるけど。)

↓ここでいうと。

http://www.altima.jp/column/fpga_edison/io_std.html

表中のVCCIOが同じものは同じバンクで使用できるが、

異なるものはバンクを分けて、

それぞれのバンクのVCCIOに指定の電圧の電源を入れる必要がある。 ついでに、入力ならIO電圧は関係ないことも多い

きっちり把握してないが、LVCMOS入力ならIO電圧は何でも良かったような気がする

あとはデータシート見れ >>751 の訂正です。

すみませんでした。

Spartan6はLVDS_33のサポートがありますので、

必要なLVDSが3.3Vで、VCCOを3.3Vにしておけば、LVCMOS33出力も同一バンクでできますね。

ここしばらく取り組んでいたLVDSが2.5Vだったので、つい、頭の中が、LVDS = 2.5V以下 みたいなふうになっていました。 LVDS33なんてあるんだな

2.5か1.8だと思ってたわ

まあ、相手がいないから同じFPGAとしかせつぞくできないかもね LVDSって、SelectIO 部分で、1つの信号を非反転Buffer 反転Bufferに入れて

Skew調整しただけじゃないの? >>757

出力バッファーに、アナログオペアンプ回路ぐらいあるんでね? オペアンプは、いらんだろうが、

Low Voltageなんだから、電圧を下げなきゃいかんのじゃないか。 LVDSのドライバって俺が知ってるのはこんなのだよ。

VCCの電圧にかかわらず、差動電圧は350mVになる。

FPGAの中で、これじゃない実装になっているかどうかは知らない。

>>757

>>757

alteraの話だけど(たぶんXiとかも同じじゃないかな)、

単なるLDVS指定はちゃんと差動バッファ使ってる。

LVDS_3Rとかはそんな感じらしいね。 >>768

面白いな。

ただ、原理的にTrの使用効率が悪そうだな。 >>773

サンクス

>>772

コストはFPGAの10分の1以下って主張してるね そりゃ今はしょうがないべ

売りたきゃ自分らで頑張って作るか、

仕様をオープンにしてサードパーティー巻き込むかしかない ブロックRAMへステートマシンをインプリメントするってヤツみたいなもん?

論理合成に時間かかったんじゃないかな

今は知らんけど > MRLDの回路構成はニューラルネットとも相性が良いことから、今後は人工知能(AI)の用途も狙っていく。

確かに、信号のやりとりが近場のヤツとだけで済むような用途には向いてそうだな

メリット出せるのは、そういった類の特定用途だけそう

んでも、この手の市場が今後デカくなるってなら 意味有るアプローチだな 新しい技術とは?

古い技術がベースでない技術とは? これに対抗してFPGAの値段が下がってくれるとこっちはおいしい xilinxから手鏡を貰ったのだが、おっさんしかいない職場に手鏡を配ったって使わんやろ…… FPGAを淘汰できるくらい使いやすいデバイスだと俺はおいしい >>790

そんな夢のデバイスなら誰でもおいしいやろ altera de10-nanoについて教えて頂きたいです

ボードとUSB Ethernet接続をして、ウェブサーバーのチュートリアルページを10分くらい開いていたらFPGAが異常に発熱していました

時間を置いて接続し直しても異常に発熱します

これはよくある事なのでしょうか? >>792

そもそもそのFPGAは何をしているんだい?

USB-Ethernet変換器? FPGAにWebの動画を再生させていたってことか? de nanoは本体のromにマニュアルとLinux保存されてて、USB Ethernet経由でそいつにアクセスできるみたいな仕組みだったはず へーそうなんだー

ということはボードは動画を転送しているだけで、再生してるのはパソコンか

なんで発熱するんだろ Linux回すとかなリ食うらしい

ヒートシンク&ファン何も無しなら、Pi3でもmake -j4 であっという間に70℃超えるから

そんなもんでしょうな

更にGPU無しなら描画廻りは全てCPU負担。 フルで回りっぱなしならそんなモンじゃない

ヒートシンク&ファンでも付けるか、ssh程度で我慢するか、FPGA部分のみ使うか・・・

そんな処だな。 ぶっちゃけ言うと内蔵ARM 大した価値無い。 個人的にはssh程度で十分なんだけど、GUIあった方が新規増えるかもな Vivadoで訳あってBRAMを使わずにSliceのリソースだけで実装したいのですが、Synthesis Setting で-max_bram 0 にしてもわずかに消費してしまいます。

BRAMの使用を強制的に無効にする方法ないですか?

ちなみに現在下記のようなWarningが出ています。

[Synth 8-3323] Resources of type BRAM have been overutilized. Used = 6, Available = 0. Use report_utilization command for details. >>802

回路関係無しに、何かしらに使われちゃうのかね

やり方は合ってそうだけど >>802

場所を特定して

(* ram_style = "distributed" *) 初心者なんだが昔に買ったDE0+Quartusで勉強してみたい

目的はデジタル回路の理解とFPGAを使ってみたい程度のレベル

DE0の後継でCVとか出てきてるんだが、このぐらいの用途ならDE0でも問題ないのかな? >>806

全然問題ないよ。LEの数が少ないけど、一通りペリフェラルついててちょうどいい >>807

レスありがとう!安心しました。

HDLとか設計も未経験なので本をなぞりながら勉強しようかなと

デジタル回路はストップウォッチの動作をなんとか追える程度の学生レベル

なので焦らず自分のペースでやってみますわ DE0でも十分、8bitパソコン一台収まる位の規模までいける >>809

ありがとー!

quartus2のインストールとボードの動作確認まで完了したよ

ボード付属のCQ出版の本読みながら頑張るよ >>810

健闘を祈る。そして日本を担う技術者になってくれ >>811

俺そんなに若くないから無理w

おっさんの趣味と思ってくれ CPUコアから自作モジュール(Verilog)を呼び出して実行するのってどうやるのが一般的なんですか?

AXIはVerilogで実装するのが面倒なので、Dual-Port BRAMを挟んで、0番地の0ビット目で実行開始を指示しています 自分でFPGAのボード買おうと思うんだけどPapilio Pro LX9ってやつがいいの?

1〜2万円台で買えるFPGAボードで流行とかおすすめあったら教えてください。宜しくお願いします。

超初心者なんで参考書とかもあったら合わせて教えてもらえると有難いです。 それググれずに開発時のトラブルが解決できるだろうか >>817

貴重な情報をありがとうございます。

APBスレーブとして動作する適当なモジュールを自作してみたのですが、

なんかAXI to APBブリッジとの接続トラブルっぽいのが起きたので、

しばらくエラーと格闘します… >>816

まぁPapillioで良いんじゃないか?

CPU付きに興味あるならZYBO(秋月のライセンス付き)でも MAX10 論理合成と、クロックのスキュー少し悪くないですか?

時々変なの FPGAって将来的に個人ユースで普及してくかな?

AIエンジンに向いてるのは判るけど

h.265エンコーダーとか動画用としてはどうなの?

そっちは今まで通りASICかGPUのどっちかなんだろうか? 開発費が回収できないから、数が出ないのヤツはFPGA

出ると解かってるなら迷わずASIC

h.265

もとから効率悪いのに、逢えてFPGAで組むヤツいるか?

どう足掻いても ASIC or GPU の価格に対して勝ち目無しだし

AIエンジンの類だって、数が出るようになればASICに置き換わるわけだし

主戦場は、今後もニッチ市場だろ そんな事自分で判断できないレベルの人がAIのロジックなんか組めないw マクロで見れば永遠にニッチなのは当たり前だけど、

ミクロで見れば過渡期のアルゴリズムを扱う事が多いならFPGAが主流にだってなるだろ。

AIなんて良い例だ >FPGAとCPUのスピード比較ってないかな

比較にならんので比較するまでもないだろ。

それより最高速、最新のFPGAでMAXどのくらいのクロックで動かせる? カップ麺の製造スピードと、クルマのスピードを比較しても仕方がない。 >設計によるとしか

デバイス性能を聴いてるのだから設計にはよらんと思うが、、、

「まあ500Mhzも出せんだろ」くらいにしか思っていないのでそんなに期待してるわけでもないが、、 >>836

何を動かすかによってスピード変わりますやん。

単純なレジスタ1個のトグルスピードを知ったって意味ないと思うし。 CPUが早いならソフト開発までで終わってオマンマ食い上げじゃ。 Clock Tree Performance for Stratix 10 Devices

Programmable clock routing 1,100 MHz

>>836

良い線言ってると思うな

実際、意味の有る回路組んだら、せいぜい この 1/3 ぐらいだろ もう何年も速いデバイスは触っていないが、Ghzまで進歩したのか。凄いなとは思うがCPUが速すぎて

やっぱり見劣りするな。 >>840

CPUじゃ同時計算、最大でもスレッド数が上限だがFPGAではゲート数内で幾らでも増やせる ありきたりだが、アプリケーション次第としか言えんよな でも10コアが普通に3.3Ghzで動くからな。1.1G換算なら30コアだからなー。でも実質となると

さらに3倍くらいだとすると、90コアだな。

CPUとそれに匹敵するには機能てきにはCPU90コア分くらいと同等のロジックがFPGAに入るかってことになるが

どうなんだろう? 既存CPUまたは、既存CPUでやっていることをFPGAで置き換えようとするような比較をすることが無理があると思うんだけど。

確かに、そういう用途も出てきてはいるけれど。 >>841

スレッド数っていうか、コア数ね。

まあ用途によるとしか。 >>843

さすがにそれはむりじゃね?

それができたらCPUはFPGAで組めばいいことになる FPGAってのはロジック部より配線部の無駄が多いICだよ。

使うか使わないか分からない結線を一杯用意しておかないと

ユーザが組みたいロジックが接続できなくなる。

それでもFPGAがASICを置き換える事が出来るのは、

イニシャルコストが小さい事とTATが短い事がASICには無理だからでしょ。 論理修正もバカ高いマスク費かからんしな。

心臓に良い。 大昔は〜10枚セットで1千万くらい。ちょっと前、聞いたのは24、5枚で4億強

自分が最後にASICやってたのは1億くらい。 そういやミニマルファブは順調なのかな

ASICの直描は不発だったがレチクル屋に縛られるのもなぁ 素人というかは微妙だけど物理屋さんが自分らで計測器つくるのにASIC作ってるのは聞いたことがある うちの会社の素人さん達が数百万円でASICを作れるなどとアホな事言って、俺に開発を丸投げしようとしやがる。誰か俺の代わりにぶん殴ってやってくれ。 設計ソフトやらIPやらで製造以外のほうが金掛かりそう

外に見積もり出してみてプロですら手こずるってことを示す? オレは元々ASIC屋で彼らもそれは知ってるはずなんだが、そんな金額では作れないと何度言っても、お前がヤル気が無いだけだろうと言われてしまう。

彼らは仕様もまともに検討せずに、ASICを作れば良いものが出来ると言って作ることが目的になっている。それで自分は有用な提案をした気になってるから頭にくる。

上にいるのは口先だけのご機嫌取りばかりなので、今の会社は半分諦めてる。良い会社あったら教えてくれw 最近の事情は知らないけど、

プロセスにも依存するがシャトル使えば数百万で作れるんじゃないかな。

ただ、TATは長いし、ちょっと間違えたって言うとまた同じ費用が必要。

徹底的にシミュレーションでバグつぶさないと

OTPのマイコンどころじゃない屍が溜まるぞ。 そいつらの言ってるASICってFPGAのマスク版ではなくて? "プロセスにもよる" ってんだから、30年くらい前のものとか

或いは、インターポーザーとか

数百万で出来るったら、せいぜいその程度の物

マトモナASICのマスク費用なら、 おおよそ>>856 言ってる通り

だが、そのマスク費用より、量産後のバグの方が遥かに深刻

不安で夜も眠れなくなるよ >>868

今頃ソフトのライセンスとか書き込み機でシェアを取ろうと考えてるんだろうなぁ……。

ソフト無償位はしてもらわないと特殊用途向けだけで儲かりはせんだろうね。 0.35μのG/Aとかなら安いんじゃね

RAM必要とかだとG/Aじゃアレだが

バグは設計した部分は案外大丈夫なんだけどIPで化かされるとなぁ 瞬発力が必要なんでクロック上げる必要があるけど

必要なのは1秒のうちの0.2秒ぐらいなんだけど

NIOSで組込みマイコンの様にCPUが暇なときに

クロック落としたり止めたりできないのかな。 >>871

クロック落としたり、止めたりすればいいんじゃね

もまえ、アボガド >>871

「NIOS クロックの動的制御」でググると何か見つかるかも ハードで制御するもんなの?

sleep すればいいんじゃない。 FPGAマスク版ってFPGAの性能100パーセント保証って認識でok? tpd からなにから同じだと謳ってますが、使った事ないので実際どうかわかりません。 ストラテックスのDSP物理コア付きの開発評価ボードって今安いのでいくらで買える?

あと、IPだけを提供してる会社はどこが良いかね?個人レベルで買えるところが良い。論理合成は自分でやる前提で。

久しく遠ざかってました。 >>879

MAX? できればストラテックスがいいのだけど。 釣りだと思うけど、Terasic あたりで好きなの買えば? >>881

何で釣りなん?こんな釣りして何のメリットが?w

秋月のキットってザイリンクスの奴か?これDSPとは書いていながらFLOPSか何かもわからん。

GPGPUだと高性能だと、10TFLOPSとかじゃん、このレベルを出せるのはストラテックスしかないんじゃ?

まあ、ストラテックスは極端かもだが、めいいっぱいGPGPU IPコアおてんこ盛り&浮動小数点数演算を物理DSPで計算させたら結構凄いのができないかな?って妄想はしてるんだ。

ストラテックス評価ボード80万円位?

28nmやら14nmプロセスってなんだよ。。。

俺は360nmしか知らねーよ。 >>879

>>>878

>秋月電子で1万円ぐらい

de0-nano-soc 物理DSP ってのは、ただの浮動小数点演算か?

お前にはこれで十分だろ "ストラテックス" ってなんだ?

もしかして、 Stratix の事か 違うよな >>884

まあね、多分じゅうぶんだとは思う。

ベリログもう忘れちまったなぁ。。。

知らないのもあるし。

>>885

当時は皆そう呼んでた。 浮動小数点演算なら、Stratix より Arria10 だな

安めの中古車くらいの金額で評価ボード売ってるよ >>887

それが現実的かなぁ。

ゲート数もミドルエンドで有りながらそこそこあるし。いまのところ検証ツールも何も持ってないお。

ところで、言語設計者が人手不足過ぎないか?ホビーを中心としたコピペ似非ロジック設計者で開発営業マンの漏れにも、仕事の依頼がきて困ってるのだが。

誰かやってやれ プログラマを連れてきてCで書けば回路にしてるれるんだろ。

な、Xilinx さんよ。 >>889

派遣会社通さないで月100万円払うならやってやってもいいぞ

派遣会社通すなら月200万円な

嫌なら自分でヤレヤレ >>892

フリランさんでも100なら出すんじゃないかね?某画像処理関係。

もちろん一人で全部やるわけじゃないけどね。ASIC前提だから中身は重たいよ多分。 cyclone10はスレ的にどうなのよ

いろいろFPGAがあるけど個人でdeeplearningの量子化ってのをやりたいんだけど

選定方法とか少し教えてくれない。なるだけ安い奴。 >>896

FPGAの選定が出来ない時点でお前には出来ないで、下請けに丸投げするのがとどのつまりだから安心しな >>896

ゲート数、RAMブロック数、ペリフェラル、値段 特別なハードウェアが必要でない限りはどのFPGAも本質的に同じだから出来ることと性能に大きな違いはない Intel modelsim に xilinxライブラリ読ませたら幸せになったw >>868

お得意の人工衛星・航空宇宙用以外にも、軍用とか原子炉制御とか、放射線の問題がある使途はたくさんあるから、数は捌けないけど異常に高い値段で売れるかもね。 放射線といえばXのウルトラスケールに使われてるFinFET技術は構造上放射線にすこぶる強いと聞いたことがある Actelジャナイと!ダメだろ放射線は

クソ遅いけど いにしえのアンチヒューズ型FPGAかいくらかは強いと評判のフラッシュ型か

それはともかく今はマイクロセミじゃなかったっけ 作ったらその後弄らない前提ならクイックロジックが速かったなぉ。

今はどうなんだろ? >>906

ミスったチップがどんどん溜まるクイックロジック。

プログラミング中にミスに気づくことしばしば。 ちゃんとシュミレーターでデバッグせえや。勿体無い。 シミュレーションを十分やったはずなのにたまに発生

さすがにいつでもってわけじゃないが長くやってれば溜まってくる

溜めといても何かに使えるわけじゃないからさっさと捨ててしまえばいいんだが邪魔になる程の量でもないから記念品みたいに残ってる いいアイデアだけどキーホルダーがたまっていきそう・・・

ああ、邪魔になったら捨てればいいのか 昔の紙テープみたいに駄菓子屋に卸す?

でも、今時の子供だと書き損ないチップなんぞ遊び道具にならんか。 趣味リフローの練習用チップとしてどうかな?

専用ボードとセットで

もっとも、ちゃんと付いたかどうか、どうやって確認するか?って

問題があるけどw >>914

端子と基板をテスターで繋ぐ。

QFPは手付けするのが職人ってもんさ。

付けるより外す方がテクニック必要だけどね。 >>913

紙テープなら読んで「怪獣が荻原公園に出ました」って遊べるけどチップじゃあそべないよな うちのガキが小学生の頃、ジャンク箱から見つけた❗DIPのICをセロテープで10個ぐらい数珠繋ぎにして電車ごっこしてた

コードで軌道、ケミコンやリレーをよく分からない施設、建物にしてジオラマのつもりだったらしい。

写真撮っとけば良かったと今思うが、当時は発見した妻の箒であっという間に消滅してしまった。

子供は空想力で何でも遊びに出来るんだよな、裏山すぃい。 国産量子コンピュータ、FPGAが入っててるもんで、なにやら研究者たちが騒いでるな あれは量子コンピュータとは呼べないとか、

FPGAだけで作った方がもっと安くて安定したのができるとか。 >>920

最近文科省が押すものにアヤシイものが多い。

GYOUKOUとかエセ量子とか。

こんな形でガラパゴス山のエセ大将やってていいのか? 巡回セールスマン問題用のfpga(asicのほうが近いか?)を考えてみたんだけど、

もしアイデア自体に問題がなく、

巡回セールスマン問題をかなり高速で解けたとして、

需要ある? ランクが下がれば需要がある。ランクが下がらないなら世界のどこかに既にある。 概要:添付の図(https://imgur.com/a/tiPiJ)のような樹形図回路を用意、

分岐をある地点からの選択肢とする。

また、地点と地点の間は距離に見合った(比例した値の)抵抗を置く。

そして中心から電気を流し、末端に流れる電流量の最大を測定するなり、

アナログ的に比較するなりして最大値を求める。

これを地点数の分だけ繰り返し、それぞれの最大値を取った経路のみをパソコンで演算すれば

格段に演算量が少なくなる。

原理:アナログ回路を上記のように組めば、電気が伝わる速さで結果が出せる。

(抵抗値の合計が最も少ない経路に、最も多くの電流が流れるため、演算の必要なし。)

ただし、とても多くの可変抵抗を組み込んだ専用回路を必要とする。

可変抵抗数は簡単な計算の結果、総当たりに必要なパターン数の約三倍くらい必要な模様。 利点と問題点:

概要に記載したようにすると、パソコンによる地点数ぶんの演算は必要だが、

初めから全パターンを探索も可能。

(ただし、完全なる逆走パターンも同じ値をとるため、その検出が面倒かと思った。

また、可変抵抗数はさらに「×地点数」という量が必要になる。)

メモリ領域へのアクセス数が明らかに減る。

現在のパソコンだと、

1.メモリからの読み込み

2.cpuの演算

3.メモリへ演算結果の書き込み

という工程が必要だが、

このfpga的なものだと

1.メモリへのアクセス

だけで終わる。

また抵抗値の値のパターンは「地点数C2(2は小文字)=地点数×(地点数-1)/2」パターンしかないので、

かなり前の世代のcpuのキャッシュ領域ですら保存できる可能性が高い。

(もちろん地点数をあほみたいに増やせばあふれるけど)

つまり高速アクセスが可能。

ここから先はキャッシュ領域やバス幅を増やせば加速度的に早くなるけど、割愛。 要約:

総当たり演算の代わりに多数の可変抵抗を準備というトレードオフによって結果を求める。

しかし、可変抵抗の準備にかかる時間は現行技術で十分高速化が可能ある。

演算時間において、デメリットよりメリットのほうが大きいため、

かなりな高速化(地点数が十分多いときにおいて)が見込まれる。

問題点として、汎用性が低いこと、製造コストが少し高めになってしまうこと、

などが考えられる。

補足:

図の場合だと、5点を巡回するので、

初めにある点をスタートと決め、

次の選択肢は四つあることになる。 ハード量が問題だよね。

10箇所のとき、20箇所のときで、抵抗何個いるの? 総パターン数のおよそ三倍ということに間違いがない場合、

10地点で1000万個ぐらい。

20だと7500000000000000000個ぐらいかな。

ちなみにCPUのトランジスタ数が

5500万個という記述があったので、

(https://oshiete.goo.ne.jp/qa/7602697.html)

11地点までくらいなら作れなくはないかも程度。

ちなみに、http://www.geocities.jp/m_hiroi/light/pyalgo62.html

に記載されている感じだと11地点で6分ぐらいかかりそうなので、

技術的な落としどころ(製造可能な範囲)と、社会的なニーズ(6分判断待ちはできない)

が合いそう。

また、明らかにあり得ない組み合わせを排除するアルゴリズムが

何個か開発されていたはずなので、

それを用いると抵抗の数を減らせるはず。

あるいはパターン分けを行うという手もある。

例えば明らかに離れた二つの集団(10+10)がある場合、

初めに片方の集団だけを検討し、次にもう一方の集団だけを検討、

最後に総合評価で出せば、20地点でも対応できる。

(さすがにこれは都合がよすぎる場合だけど) 分枝限定法は探索木を深さ優先で直列に調べていって

調べる必要がないと確定した枝は破棄する方法なので、

完全並列を目指すこの方法にはほとんど適用できないよ。

あと、最後の比較もちゃんと考えないと死ぬよ。 >分枝限定法は探索木を深さ優先で直列に調べていって

>調べる必要がないと確定した枝は破棄する方法なので、

>完全並列を目指すこの方法にはほとんど適用できないよ。

そうなんですか・・・

不勉強でした。申し訳ないです。

例えば、11地点用の回路が製造できたとして、13地点で検証したい場合、

13×12回この回路を回せば、そのあとに13×12通りの演算をパソコンですればいいだけになる

と思うのですが、その場合の計算数を減らせるかな、とも考えていました。

ただ、この場合演算数が少ないので、わざわざ別プログラムでやる必要がないですね。

>あと、最後の比較もちゃんと考えないと死ぬよ。

そうなんですよね・・・

24bitで計測可能、18bitまでは確実に正確!

みたいな計測IC的なものを用いたほうが楽ですかね?

上位ビットから確認していって、一番「1」が続くものをピックアップみたいな感じで。 TSPは各点で異なった高さにテープを貼った鏡を回転させて待っていれば答えが出る。 鏡・・・?

情報ソースはどこですか?

自力では見つけられなかったので、お願いします。 >>938

ベリログだね。

C言語に似てるからさ。

でも、今C言語でも設計できるから今後どうなんだろな。 >>938

企業は Verilog、研究機関などは VHDL みたいなことを聞いた。

特に VHDL を指定されたのでなければ Verilog でいいと思う。 自分の経験だと逆だな

うちの会社は基本的にVHDL

研究機関からの開発委託もよくあるが、それはVerilog

VHDLなのは型の扱いが厳密だから 初めてさわったのがVHDLだったから何となく。でも研究機関からきた依頼はベリログだったな。

大学だから最初は学生に弄らせる為にやはりCに似てるからそれでやるってなった。その時初めてだったから結構大変だったな。 「アルテラ」って、ちょくちょくTwitterトレンドに出てくるね

みんな好きなのね QUICKlogicフラッグシップモデルの小数点演算ってどれくらい? critical warningがぎょうさん出やがる

あータイミング制約がようわからん

キャンペーンおまけTC流さないでトレセミ行けばよかった

ドキュメントとかwebとか見てもいまいち要点が判らん タイミング制約面倒なのは確か

動けばOK、他(消費電力 or 速度 or セル効率 etc... )は気にしない

のなら、"同期設計 & クロックは一つだけ" にすれば悩まんで済む

それが嫌なら、タイミング制約を習得するしかない

近道は無いよ >>948

俺もタイミング全部見てたら大変だと思う。だから勝手に調整するロジック作って♪ >>948

僕もタイミングとか制約のかけ方が分からない。本を読んでもHDLの文法がほとんど。結局clock1つに全て同期させる、それ以外は動けばOkにしてる。

警告はだいぶ消せるけど、残ってるやつは放置してるわ。

なんかいい本とかあるんですかね。 よほど簡単な回路じゃないと警告は全部消せないだろ。 クロック一個だけなら、ツール側での状況把握が容易だから 制約付けなくても大方動くけど

複数のクロック使ったりすると、制約(ツールに伝えてやる)ツール側で判別できなから 要注意

なんの制約も無しの条件で、 回路が込み入ってセル使用率が上がって来ると、コメント弄っただけで動かなくなったりする

なんの制約も無しなんだったら、まぁ当然事だけど

何も知らない当の本人からして見れば、こう言う状態に至ったら対処の仕様が無いよな

ネットのコード見ても制約掛けてないヤツが殆どだし、趣味でやってるなら之でも良しだけど

変な目に逢いたく無ければ、単なるクロック指定だけでも 制約付ける癖つけておいた方がいいぞ

怖いのは "Hold Vioration"。 100ps 有ったら危ないと思った方がいい

制約掛けてないとその手の情報すら得られない、だから制約掛けるんだよ〜ん。 なんか、ロジック設計専用のOSみたいのとか無いですかね?素人なもんで。。まだツールとか使いこなせてないです。

なお、私は組込屋の営業マンで文系ですから理系のバックグランドは無いです。普通の回路設計やって基板化するまでは自分で全部やった事あります。

遂にFPGAに手を出してしましました。 使っているクロックはそれぞれ周波数の制約かけて、異種クロックとのつなぎはRTLでフリフロ、RAM、ハンドシェイクか、設定の書き込み中は回路止めるなどで論理的にクロック間の位相に関する制限なくせばいいだけでは?異種クロック同士は無視するという記述は必要だけど。 >>955

いや、多分それすらわかってないからw

プロに頼んだ方がいいんじゃないかな。 >>955

そのへんはまあ理解できたんだけど

端子のinput delayとかoutput delayとかが良く判らない

どこからどこ、なにからなに、いつからいつ?

仮想クロックとか訳わかめ >>953

横レスなんですけど、「組込屋の営業マンで文系」の方の手まで

借りないといけないほど、今は人手不足なのかお聞きしたいです

ちなみに、FPGAの設計自体は、微分方程式はもちろん、交流回路理論とか

過渡現象論とかもでてこないので、四則演算ができれば大丈夫かな >>958

>ちなみに、FPGAの設計自体は、微分方程式はもちろん、交流回路理論とか

>過渡現象論とかもでてこないので、四則演算ができれば大丈夫かな

その場合、たとえばデジタルフィルタの設計は別の人がやって、「FPGAの設計」をする人は

それをHDLに落とすだけの仕事って前提ですかね… >>958

私は営業ですから今は回路設計は仕事ではやりませんが、PCBの設計は社内に私しかできる人がいないのでたまにやらされます。人手不足、外注不足ですね。

過去にコピペ回路図を駆使してRFや電源のアナログの設計もやりました。FPGAはアナログ回路の要素はさほど気にしなくて良さそうですね。

FPGAもやってみたかったのですがこれまで個人レベルでは高過ぎで手が出なかったんですよ。当時の設計が使ってたツールは、シノプシスとマックスプラスだったと思います。

手前で論理設計、論理合成、配置配線、タイミング検証作業は見たことがあります。

基本的に論理設計もコピペ設計でやるつもり。 >>960

>これまで個人レベルでは高過ぎで手が出なかった

相当にこの分野からは距離を置いてこられたのかな?

Windows 3.1の時代に廉価版が出て、そこから数年ぐらいで無償版がでてきてたように記憶してます。 >>961

正確に言うと、ツールと言うよりエバレーションボードが高過ぎだったんですよ。

それこそ、秋月なんかじゃ買えなかったですから。 すでに10年ぐらい前には、雑誌の付録についてくるぐらいだったというのに。 20年前くらい。試作基板が出来てくるまではPLCCパッケージとユニバーサル基板で自分で作って確認してたな。 今は個人を相手にしてくれる実装屋が中国に出来てBGPすら何とかなるしね >>964

CPLDとかFPGAが出始めの頃は普通にPLCCやQFPだったよね。

208ピンのQFPで試作基板作った覚えがある。 DOSの時代から廉価版あったけどな。

チョッキリ10万位でPC98のDOS用エグザクト買って使ってたな。

自分で配線を編集出来て面白かった。XC2064とXC2018時代。 >>969

>チョッキリ10万位でPC98のDOS用エグザクト買って使ってたな。

ほう。それは知らなかった… アルテラがグリッド沢山のBGA出してきて基板が作れなくて困ったね。

当時基板は貫通スルーホールがメインで、スルーホール径も0.3mmまで。ピンから引き出せなかったんだよねこれが。

しかも物凄く多層構成でイニシャルも高いし、厚みをまして行く今度はスルーホールのメッキが作れないと、基板屋に泣きつかれてさ。

ああ古き良き時代。 苦労して困難を乗り越えたことが今となっては良い思い出、かな? >>964

手貼りとハトメの時代ですね。

わかります >>971

素人なんで良く分からんのだけど、今は普通のスルーホール使わないの? >>975

普通のスルーホール使うけど、0.1mmのビアが使えるようになった為、自由度が増して引き出せるようになった。

これまではBVHとかビルドアップ基板、パットオンスルーなどの工法を使わないと作れなかったんだよ。 あとね、基板アスペクト比というのがあって、基板板厚み÷スルーホールの径が6を超える基板はスルーホールメッキが作れないから、

多層板で厚みの調整が大変だったわけ。 グリッド沢山ってなんだよ

ボールピッチだろ

様々な部分で日本語が不自由なやつだな

確かに小型化要求が無ければファインピッチは避けたい

つーか最近はいろいろCR類も小型化でいよいよ1608が絶滅危惧種

村田太陽軒並み縮小方向らしい >>978

老眼には半田付けが辛い時代になったなぁ。。。0402なんて両眼顕微鏡登場させたし。

それでも付けてしまう漏れ半田のプロフェッショナル。 家で不労所得的に稼げる方法など

参考までに、

⇒ 『武藤のムロイエウレ』 というHPで見ることができるらしいです。

グーグル検索⇒『武藤のムロイエウレ』"

DRXWHOGKTE ぐわぁ

久々にVivadoアップデートしたらUIのlook&feelがゲロ変わってる!

なにもM$のクソUI(フラット?だっけ)に合わせることないだろ

こんなとこ変えて余計な神経使わせるんじゃないよ 今さ、フリーのprocessorやらGPUとかあるじゃん。こういうの使ってる人っている?

昨今ディープラーニングの話題騒然で、フリーコア使ってFPGAのみで実装して果たして満足な結果が得られるか興味ある。